# Quasi-Eight-Level Inverter with Output-Side Transformers for Single-Phase Off-Grid Electrical Energy Supply

Institute of Electrical Engineering University of Leoben, Austria

# **Kayhan Ince**

Supervisor: Univ. Prof. Dr. Helmut Weiss Co-Advisor: Univ. Prof. Dr. Karl E. Lorber

Leoben October 2010

| Eidesstattliche Erklärung:                                                                                                                             |                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| Ich erkläre an Eides statt, dass ich diese Arbeit selbständig von angegebenen Quellen und Hilfsmittel nicht benutzt und mich Hilfsmittel bedient habe. |                                   |

| Affidavit:                                                                                                                                             |                                   |

| I declare in lieu of oath, that I wrote this thesis and performed using only literature cited in this volume.                                          | d the associated research myself, |

| Leoben, October 2010                                                                                                                                   | Kayhan Ince                       |

## **TABLE OF CONTENTS**

Kurzfassung Abstract Acknowledgements

| 1 | Introduc | tion                                               | 1  |

|---|----------|----------------------------------------------------|----|

|   | 1.1 Stru | cture of Thesis                                    | 2  |

| 2 | State of | the Art in Medium Voltage Converter Topologies     | 3  |

|   |          | dulation Classification                            |    |

|   | 2.2 Sing | gle-Phase Full-Bridge (H-Bridge) Topology          | 7  |

|   | 2.2.1    | Configuration of Circuit                           | 7  |

|   | 2.2.2    | Switching States and Commutations                  | 8  |

|   | 2.3 Thre | ee-Phase Two-Level H-Bridge Topology               |    |

|   | 2.3.1    | Configuration of Circuit                           |    |

| 3 | Main No  | ew Contribution                                    | 13 |

|   | 3.1 Qua  | si-Eight-Level Inverter                            | 14 |

|   | 3.2 Con  | nparison to Conventional Systems                   | 17 |

| 4 | Modelli  | ng of Quasi-Eight-Level Inverter                   | 18 |

|   | 4.1 Mod  | dulation Method                                    | 22 |

|   | 4.1.1    | Sine-Triangle Modulation                           | 22 |

|   | 4.1.2    | Discrete Implementation.                           | 30 |

|   | 4.1.3    | First Inverter                                     | 31 |

|   | 4.1.4    | Second Inverter                                    | 32 |

|   | 4.1.5    | Third Inverter                                     | 35 |

|   | 4.2 Pow  | ver Losses                                         | 40 |

|   | 4.2.1    | Compact Power Semiconductor Model                  | 40 |

|   | 4.2.2    | Conduction and Switching Losses.                   |    |

|   | 4.2.3    | Selection of Heat Sinks                            | 41 |

|   | 4.3 Con  | clusion                                            | 43 |

| 5 | Modelli  | ng and Simulation                                  | 45 |

|   |          | ematic Description of the System                   |    |

|   | 5.2 The  | Structure of the System                            | 49 |

|   | 5.2.1    | Permanent-Magnet Synchronous Machine               | 51 |

|   | 5.2.2    | Algorithm Analysis                                 |    |

|   | 5.2.3    | Rectifier Models                                   | 57 |

|   | 5.2.4    | DC Link Capacitor Models                           |    |

|   | 5.2.5    | DC Link Voltage                                    |    |

|   |          | ign Criteria and Converter Data.                   |    |

|   |          | Power Semiconductor Devices                        |    |

|   | 5.3.2    | Influence of Wiring Inductance on Switching Losses |    |

|   |          | ation Transformer Model                            |    |

|   | 5.4.1    | Single-Phase Transformer Model                     |    |

|   | 5.5 Loa  | d Model                                            |    |

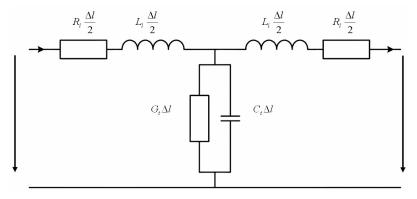

|   | 5.5.1    | Cable Model                                        |    |

|   | 5.5.2    | Shielding                                          |    |

| 6 |          | nental Layouts                                     |    |

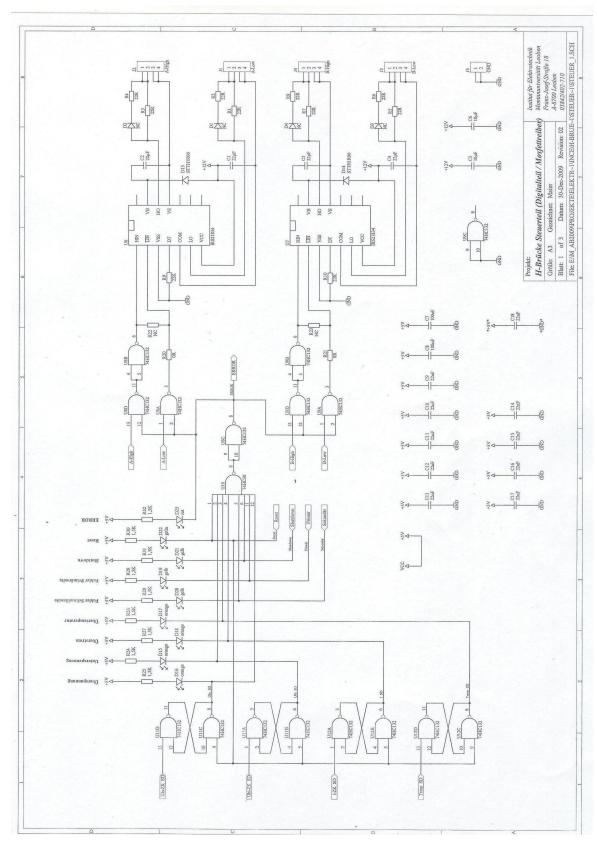

|   |          | trol System Hardware Description                   |    |

|   | 6.1.1    | Controller Board                                   |    |

|   | 6.1.2    | Digital Signal Processor and Control Hardware.     | 83 |

|    | 6.2   | Software                                        | 84  |

|----|-------|-------------------------------------------------|-----|

|    | 6.2   | 1 Implemented Algorithms                        | 84  |

|    | 6.2   |                                                 |     |

|    | 6.2   | 3 Protection Concept                            | 87  |

|    | 6.3   | Converter Comparison                            | 90  |

|    | 6.3   | 1 Comparison of Power Semiconductor Utilization | 90  |

| 7  | Co    | nclusions and Future Work                       | 115 |

|    | 7.1   | Conclusions                                     | 115 |

|    | 7.2   | Future Work                                     | 116 |

| 8  | Bib   | liography                                       | 117 |

| 9  | Lis   | t of Figures                                    | 124 |

| 10 | ) Lis | t of Tables                                     | 129 |

| 11 | Lis   | t of Abbreviations                              | 130 |

| 12 | 2 Ap  | oendix A                                        | 133 |

|    |       |                                                 |     |

# Kurzfassung

Vor Ort verfügbare erneuerbare Energiequellen sind ideal für die Bereitstellung der Stromversorgung in entlegenen Gebieten geeignet. Gegenwärtige Lösungen erfordern hohen Aufwand an Leistungselektronik und deren Ansteuerungen, um eine gute Qualität der Ausgangsspannung zu erzielen. Diese Arbeit beschreibt das Design und Layout einer speziellen einphasigen Stromversorgung mit einer hohen Spannungsqualität und einem geringen Aufwand an Leistungselektronik durch Anwendung eines speziellen Quasi-Acht-Punkt-Wechselrichters mit Hilfe einzelner H-Brücken.

Zunächst werden die verschiedenen Möglichkeiten der Umsetzung eines mehrstufigen Wechselrichters für netzgekoppelte und seine Stromversorgung untersucht und die Vorteile und Nachteile der jeweiligen Lösung ausgezeigt und ein H-Brücken-Modul entworfen und gebaut. Mithilfe diese Module und einigen innovativen Konzepten wird ein Modell eines mehrstufigen Wechselrichters entwickelt und eine Reihe von vorläufigen Messungen durchgeführt.

Unsere neuen Erkenntnisse haben Vorteile im Vergleich zu anderen standard Multi-Level-Wechselrichter-Topologien. Gemeinsame Ansätze haben Trenntransformatoren mit Delta-, Stern-oder Zickzack-Wicklung Verbindungen. Der komplexeste Teil ist, um die benötigten Parameter wie Induktivität und Widerstandswerte des einzelnen Transformators zu bestimmen. In dieser Arbeit werden alle Wechselrichter durch einen gemeinsamen Zwischenkreis eingespeist. Die Transformatoren sind am Ausgang der Wechselrichter, der die primäre Seiten jedem Wechselrichter parallel geschaltet und die sekundären Seiten in Reihe geschaltet sind. Gruppierung von diesen sieben Transformatoren als 1, 2 und 4 können insgesamt Spannungsebenen hergestellt werden. Bezugnehmend Sinusförmigesspannung, jede Gruppe von Transformatoren funktionieren unterschiedlich in einer Periode. Daher der Klirrfaktor und die Verluste der Wechselrichter bestimmen Schaltzustände dieser drei Gruppen von Transformatoren. Schaltfrequenzen zwischen 4 kHz...20 kHz, sind die wichtigsten Arbeitsbereich des MOSFETs Wechselrichter und experimentellen Ergebnisse zeigen, besser Ausgangsspannung mit zunehmender Frequenz.

Diese Vorteile verhindern Filter Umsetzung welche in der Regel eine gemeinsame Lösung ist und auch eine Verringerung der Kosten bei dieser Art von Systemen.

#### **Abstract**

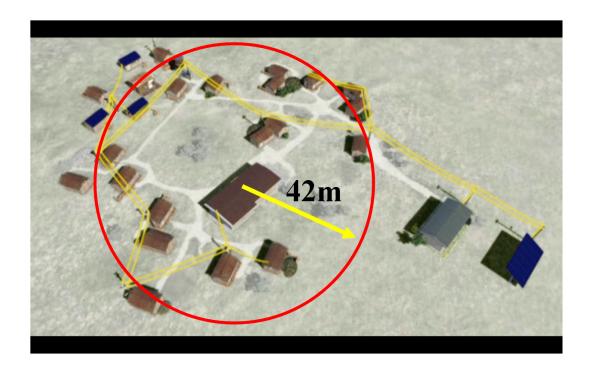

Renewable energy resources available locally are ideally suited for providing electricity supply in remote areas. This work describes design and layout of a special single phase supply system with high voltage quality and low power electronics expenditure through application of a special quasi-eight-level inverter output voltage shape with H-bridge circuit configuration. The task is to minimize the number of stochastic and unknown parameters influencing the device functionality.

First, the different possibilities to implement a multilevel inverter for grid and its power supply are explored, pointing out the advantages and disadvantages of each solution. Then, an H-bridge-module is designed and built. With these modules and together with some innovative concepts a model of a multilayer inverter is developed and a set of preliminary measurements are gained.

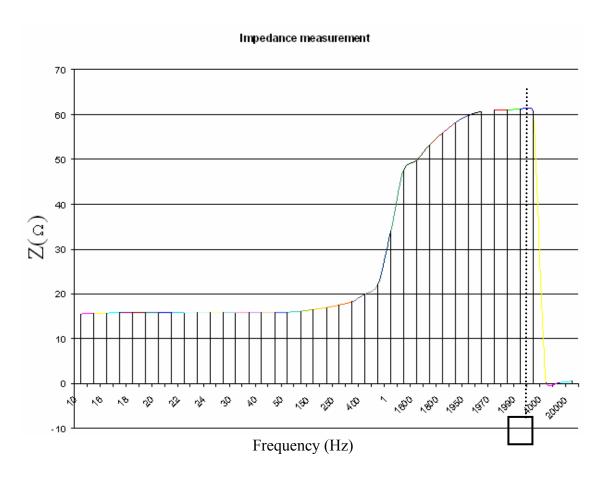

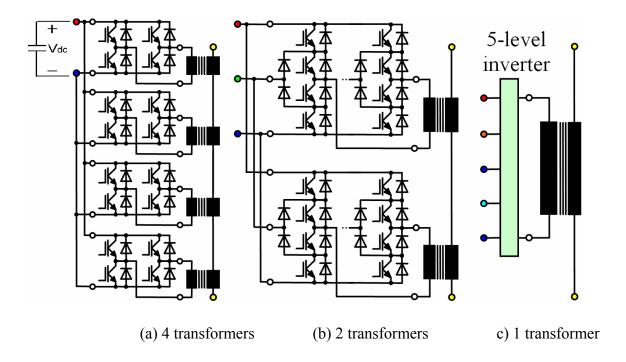

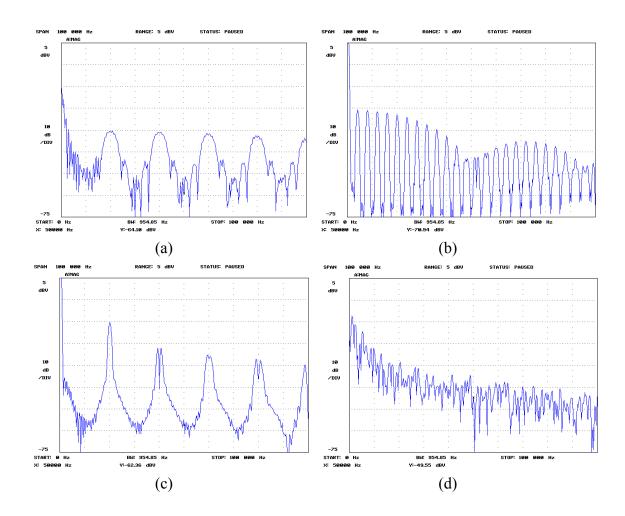

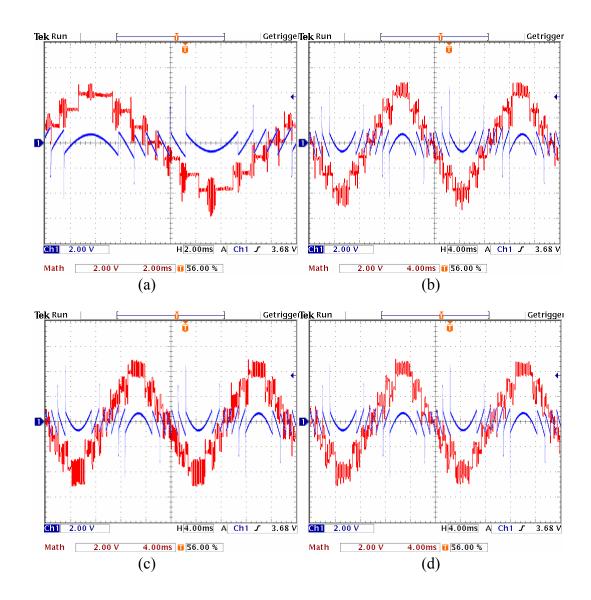

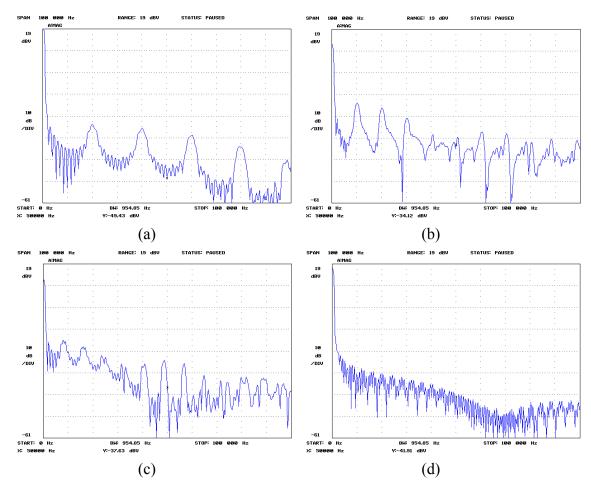

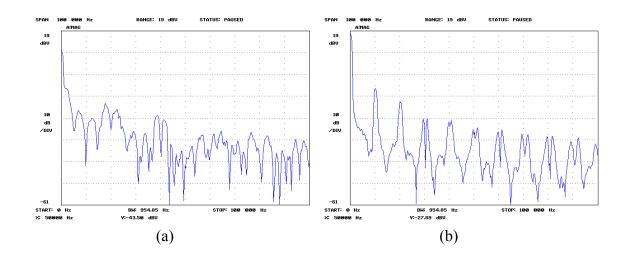

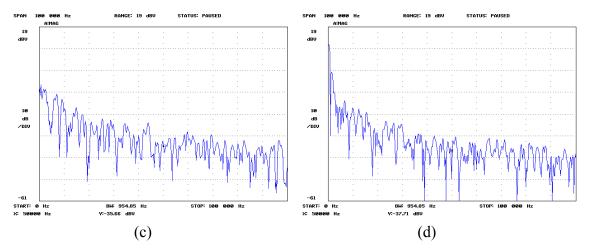

Our new contribution has advantages compared to other standard multilevel inverter topologies. Common inverter approaches have isolation transformers with delta, star, or zigzag winding connections. The most complex part is to determine the needed parameters such as inductance and resistance values of each transformer. In this thesis, all the inverters are fed by a common DC bus. The transformers are located at the output side of the inverters which the primary sides are connected to each inverter in parallel and the secondary sides are connected in series. Grouping of these seven transformers as 1, 2 and 4, total 7 voltage levels can be produced. Referring to sinus voltage, each group of transformer acts differently in one period. Therefore, switching states of these three groups of transformers determine the total harmonic distortion and losses of the inverters. Switching frequencies between 4 kHz...20 kHz, are the main operation area of the MOSFETs inverter and experimental results show better output voltage with the increasing frequencies.

These advantages prevent filter implementation which is usually a common solution and also decrease the costs in such kind of systems.

# Acknowledgements

First of all, I thank God for this possibility to live such a good experience in my life.

I would like to thank my advisor Univ.Prof. Dipl.-Ing. Helmut Weiß for his arrangements, supervision, reading and correcting my work. I am very grateful to Univ.Prof. Dipl.-Ing. Karl Lorber who initialized the contact and lead the support. I would like to thank Mr. Maier for his support and patience during the production of inverters. The materials were supported from the institute of electrical engineering in design and testing phases.

I am also grateful to my wife Seyda for understanding me and for her support during all these years and to my mother and sister for all the help they gave me, a support both monetary and moral.

I want to thank all friends at once, because these pages would not be sufficient to contain a punctual description of the reasons why I have to thank each one among the friend of mine. The experience in Austria made me meet new people whom I consider friend. I want to keep in contact with them all; their friendship made me grow and helped me during my stay in Leoben.

Kayhan Ince Leoben, Austria, 08 August, 2010

#### 1 Introduction

In the period from 2003 to 2008, wind power capacity increased from 40GW to 120GW, solar photo-voltaic power capacity increased from 2GW to 13GW [24]. Continuous improvements are urgently needed in all industrial and consumer applications. This is the case of a large number of new active systems, such as wind turbines, photovoltaic systems, and others [4][6][30][46][49][121]. The new developments in semiconductors which allow an increase of their maximum voltage, current and switching frequency, investment reduction, reliability, quality of output voltage, in such a way that it is possible to design efficient and reliable Voltage Source Converters for Middle Voltage applications [8][10][34][62]. Among these designs, two-level Voltage Source Converter (2L-VSC) with active-front-end and transformer configurations is mainly employed and therefore, this dissertation deals with the improvement of control and comparison of these switching devices [95][121]. First, the basic operation principles and several mathematical models of the VSC are presented including some design considerations and establishing the main specifications and features of a 2L-VSC under several operation conditions.

The performance of an inverter with any switching strategies can be related to the harmonic contents of its output voltage [3][67][69][88]. As the number of input voltage levels increase, the output waveform approaches the sinusoidal wave with minimum harmonic distortion. H-bridge converter for producing an ac voltage employ switches which may be transistors (MOSFET or IGBT), or at very high power, thyristors (GTO or GCT)[5][21][33]. This thesis provides a comprehensive analysis on low-voltage converter and inverter topologies which are different in many aspects from those for high-power voltage drives, drive system configurations, and control schemes. The aim of this thesis is a new control method for low voltage converters. There is a large variety of converter models and topologies with power semiconductors (IGBTs, IGCTs, and GTOs). However, there is no application of MOSFETs converters realized and compared to standard ones viewing several parameters of new research areas.

With the development of power electronics in the recent years, the medium-voltage (MV) and high power applications have been proposed as the most competitive choice increasingly used in several industries to conserve electric energy, increase productivity and improve product quality. Many different topologies such as two-level Voltage Source Converter (2L-VSC), series connected H-Bridge Voltage Source Converter (SCHB VSC), three-level Neutral Point Clamped Voltage Source Converter (3L-NPC-VSC) have been raised from the early idea of multi-level waveforms generation.

PWM-modulated Voltage Source Converter (VSC) is more and more used as active frontends in several applications and especially in supplying variable-speed drives [29]. Multilevel topologies are frequently used mainly in order to reduce the line-side current harmonic content and to overcome the problems due to the limited rated voltages of the switching devices available on the market. In the paper a very efficient control strategy of a multilevel cascaded H-bridge VSC is presented. Depending on the maximum value of the switching frequency selected through losses or from harmonics considerations, optimized performances can be obtained in terms of reduction of the harmonic content of line-side currents and reduction of line reactive power.

#### 1.1 Structure of Thesis

Chapter 2 is a review of the state-of-the-art with different possibilities to build a number of converters and rectifiers based of the application requirements, such as power semiconductors, dc link capacitors, and transformers.

Chapter 3 discusses the Quasi-Eight-Level Inverter control operation performance for MV off-grid connected applications. The several types of multi-level inverters and configurations of transformers and harmonics cancellation seen as an input of the whole system are compared.

Chapter 4 reports the mathematical procedure used to design the main components of Multi-level Voltage source converters (VSC) which have received a lot of attention in the recent years. These converters have been proposed as the best choice in a wide variety of medium voltage (MV) applications including cascaded H-Bridge inverters. These topologies have better output voltage quality, reduced electromagnetic interference (EMI) problems, and lower overall losses in some cases. The basic converter, including the MOSFETs, modulation and switching frequency is described in this chapter is focused on modelling each component of the considered system. The frame of this chapter is also a detailed description of the simulation and experimental results which have been carried out in order to verify the proposed algorithms. The theory of operation of the inverter design is described in detail: a simulation model is built and its validity is tested against actual measurements. Mathematical models and some design considerations are presented, extending these ideas in order to select the passive electric components for 230V-4kVA operation conditions.

Chapter 5 describes the modelling and simulation of each detailed phases in this work. The modulation, losses, and efficiency of pre-mentioned converters are calculated and compared. Simulation results describe the fundamental operation performances of the AFE rectifier, mechanical system models and design criteria of the inverter and load models.

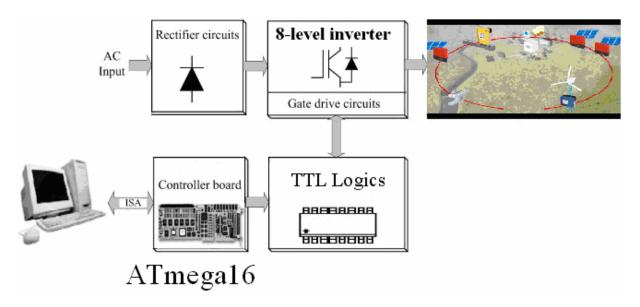

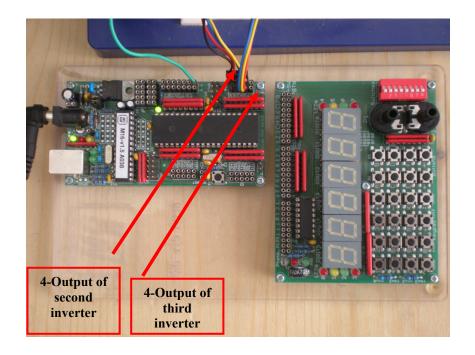

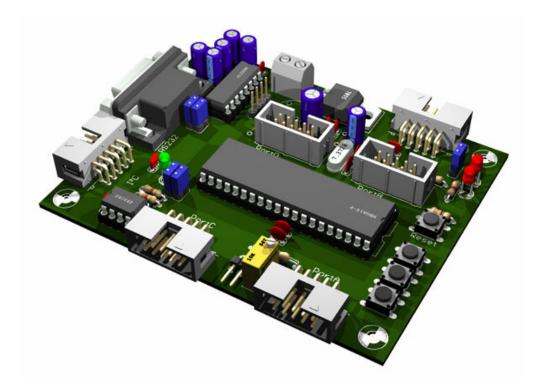

Chapter 6 is focused on the implementation of the designed control system and experimental validation; the control system is implemented in an ATmega16 platform and tested with an experimental test setup.

Finally, chapter 7 lists the conclusions and outlines the research plans for the future.

This project is focused on the control of the grid side converter and can be organized into four main parts and is divided into seven chapters which are summarized as follows:

- 1. Background and project definition

- 2. Modelling

- 3. Control system design

- 4. Implementation and experimental evaluation

This thesis focuses on feasibility of the proposed inverter control schemes of the cascade multilevel inverter, simulation, analytical and also near single-phase, practical results of a single-phase quasi-eight-level inverter design using MATLAB-SIMULINK Power System Block is carried out.

# 2 State of the Art in Medium Voltage Converter Topologies

The power limit of standard converters is given by the maximum voltage and current of a switching component [14][17]. Furthermore, a low switching frequency will provide low switching losses. An initial solution to overcome this problem was to connect several switches in series or in parallel. The series connection of two or more semiconductor devices without snubber is really difficult due to the impossibility to perfectly synchronize their switching. In fact, if one component turns off faster than the others the faster one will blow up because it will be subjected to the entire voltage drop designed for the series connection.

On the other hand, parallel connection is slightly less complicated because of the property of MOSFETs and more recent IGBTs to increase their internal resistance with the increment of junction temperature [1][113][115][117]. When a component switches on faster than the others, it will conduct all the current alone than the current it was designed for that time. But in this way, the component increases its junction temperature and its resistance. Thus it limits the current which flow through it during parallel connection state. This effect makes possible to overcome the problems coming from a delay among gate signals or from differences among real turn on time of the components.

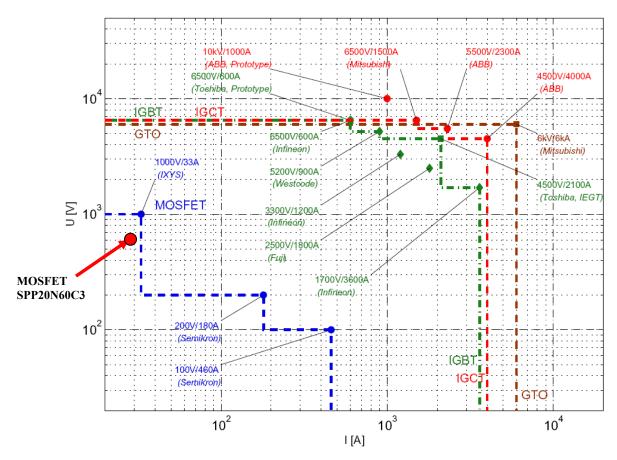

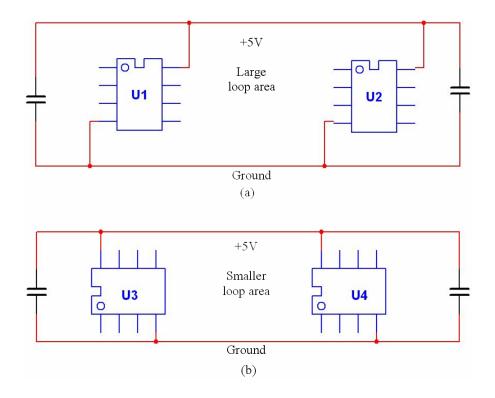

Figure 2-1: Power range of available power semiconductors [114][116]

Multilevel converters are a viable solution to increase the power with a relatively low stress on the components and with simple control systems. Moreover, multilevel converters present several other advantages. First of all, multilevel converters generate better output waveforms than the standard converters. Then, multilevel converter can increase the power quality due to the great number of levels of the output voltage, by this way; the AC side filter can be reduced. We will propose a cable of suitable length acting as filter, decreasing costs compared to a separate filter [57]. Furthermore, multilevel converters can operate with a lower switching frequency sharing the whole voltage in small steps, so the electromagnetic emissions generated by them are weaker, to comply with the standards [15][27].

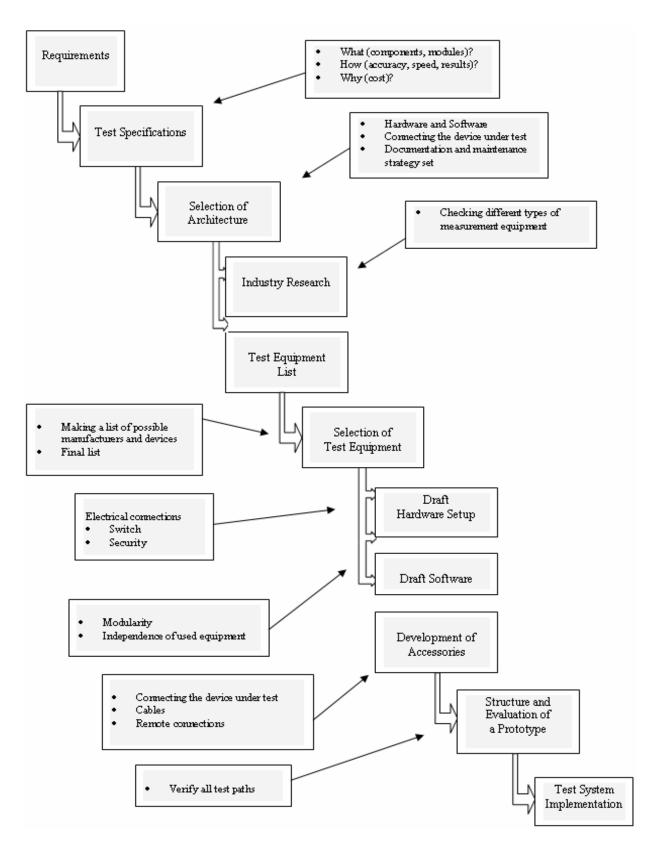

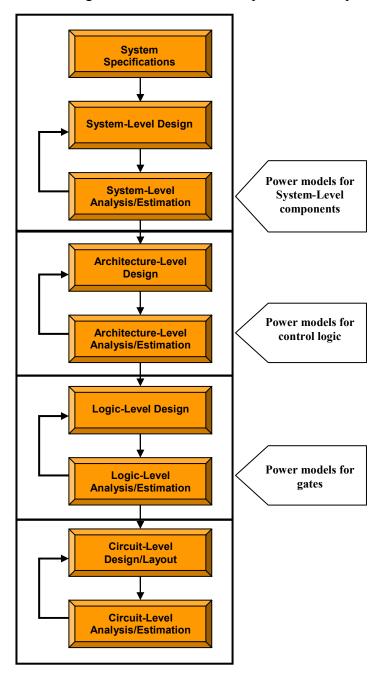

Figure 2-2 gives the methodology for designing and implementation of a system. First of all requirements must be exactly defined and test specifications including the costs should be taken in to account. Selection of architecture is the main point in a system designing. Much more time may be investigated in this phase. Measurement is also very important to prove the system reliability, searching the industry and making an equipment list.

Drafting of hardware setup is not the main issue of this work because good well-known prototypes are available in market. But, for the purpose of our implementation, we developed an inverter for possible failures which can rise during test phase. Then, with the help of simulation, several parameters are defined and results are achieved.

Structure and evaluation of a prototype is built up after having sufficient results.

Finally, test system results could be compared with the simulation and the difference between theoretical and practical ones.

Figure 2-2: Design and implementation of a test system [26]

On the other side, because of their multi-step output voltage waveforms, the total harmonic distortion (THD) of the multi-level converter voltages is relatively low compared to the 2L-

VSC. Moreover, the effective switching frequency of the multi-level converters is a function of its number of voltage levels. In other words, to achieve the same voltage THD, a higher level converter can operate at a lower switching frequency of the individual switch. Obviously, the theoretical superiority of a multi-level converter is proportional to its number of voltage levels assuming ideal switches. However, the number of voltage levels is limited by its control complexity, complication of the system structure, cost and conduction losses. The high number of switches composing a multilevel converter may lead to the conclusion that complex algorithms are necessary [26]. Fortunately, all the modulation used for standard 2-level converters can be easily adapted to multilevel converters.

#### 2.1 Modulation Classification

The modulation algorithm used to drive the multi-level converter give the voltage level required for each leg; the translation in the proper configuration of switches is done by other algorithms which can be hardware or software implemented. In this way, the modulation algorithm presented in chapter 3 can be used for all multilevel applications.

Actually, there are some modulation algorithms which produce output voltage shapes suited for particular multi-level topologies like the multi-carrier based PWM and the diode-clamped converters: in this case, the modulating signals are logically compatible with the required switches control which can be directly driven.

The aim of redundant configurations which is, to improve the switching pattern, to balance the current flowing through the switches, must be defined for the application. In general, low switching frequency methods are preferred for high-power applications due to the necessary reduction of switching losses, while the better output power quality and higher bandwidth of high switching frequency algorithms are more suitable for high dynamics applications [80][86][102][105].

At mixed switching frequency modulations, switches commutate at different frequencies, like hybrid multilevel modulation, and are particularly suited for hybrid converters [93][119]. Different cells can easily commutate at different frequencies. High switching frequency modulation is the adaptation of standard PWM to multi-levels and they are meant to switch at very high frequency, about 10 to 20 kHz [81]. Among them, there are Space Vector PWM (SVPWM) and Phase Shifted PWM (PSPWM) and a subclass called level shifted PWM. Phase Opposition (PO), Opposition Disposition (OD) and Alternate Opposition Disposition (AOD) modulations belong to this last group. SVPWM is the extension of the standard 2level Space Vector Modulation to a greater number of levels. In PSPWM several phaseshifted references are used to generate the control pulses. PO, OD and AOD exploit only one reference waveform which is compared with carriers covering all the range of reference variation [45][48][79][89]. The number of used carriers is equal to M -1, where M is the number of inverter level. Cascade multi-level inverter consists of (M-1)/2 H-bridges in which each bridge's dc voltage is provided by its own dc capacitor have been developed for electric utility applications where M is the number of levels in inverter, H is the letter characterizing the topology of a 4-switch cell arrangements [126]. However, switching losses increase as the switching frequency increases. As a result, it is desirable to select the switching frequency as low as possible.

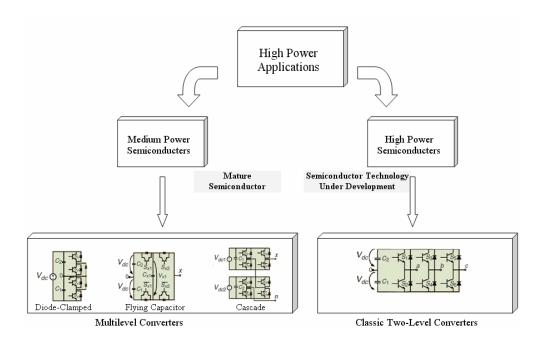

Figure 2-3: Classical two-level power converters versus most common multi-level power converters [88]

This topology requires the least number of components to achieve the same number of voltage levels. It is also possible to use modularized circuit layout and packaging because each level has the same structure, and there are no extra clamping diodes or voltage balancing capacitors which are much more efficient and suitable for utility applications than multi-pulse and pulse width modulation inverters [65]. The used condensators have big capacities and control of fixing the voltage at a certain level must be performed.

# 2.2 Single-Phase Full-Bridge (H-Bridge) Topology

#### 2.2.1 Configuration of Circuit

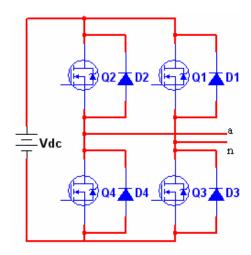

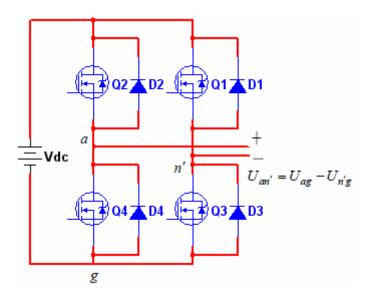

Figure 2-4: Configuration of a single-phase full-bridge (H-Bridge) VSC

The switches composed by Q1 and Q2 are the high one, whereas Q3 and Q4 constitute the low couple. The high output of one cell is shortcut to the low output of another one to realize a cascade connection between two cells.

#### 2.2.2 Switching States and Commutations

In order to produce seven levels, the switches are controlled in such away that only two of the four switches in each H-bridge cell are turned on at any time [50]. Each cell consists of two half-bridge configurations. The labels Q2 and Q1 are used to identify the transistors as well as the transistor logic (1 = on and 0 = off). Since the transistors are always switched in pairs, the complement transistors are labelled Q4 and Q3 accordingly. In order to avoid a short circuit, the complementary leg switches are not switched simultaneously. The switch positions for the three possible states of each phase leg are given in table 2-1.

Table 2-1 Three output states of H-bridges and their current paths

|           |             | Bidirectional current paths |                           |  |  |  |  |

|-----------|-------------|-----------------------------|---------------------------|--|--|--|--|

| $V_o$     | On switches | $+ip_{ph}$                  | - <i>ip</i> <sub>ph</sub> |  |  |  |  |

| $+V_{dc}$ | Q2, Q3      | Q2, Q3                      | D1, D4                    |  |  |  |  |

| 0         | OR          | Q2, D1                      | Q3, D4                    |  |  |  |  |

| $-V_{dc}$ | Q1, Q4      | Q1, Q4                      | D1, D4                    |  |  |  |  |

The current states for positive and negative phase currents  $i_{ph}$  are depicted in table 2-1. In positive "+" and negative "-" states, two diagonally opposite semiconductors (Q2, Q3) or (Q1, Q4) lie within the current path (Either two active switches or two diodes). In the second leg, Q1 is turned off first, followed by the turn-on of Q3 after the dead time. Recovery losses occur in D1 while Q3 experiences turn-on losses. Therefore, each typical H-bridge cell can only produce three distinct voltage levels. It should be noted that each of the switches must block the dc link voltage  $V_{dc}$ . The maximum switch/diode current is the maximum phase

current  $i_{ph}$ . These parameters determine the basic requirements for rating the main semiconductors.

For accuracy of switching instants, a 2-level-system has the least requirements. The only constraint is that one switch in a branch must have turned off before the second is turned on. In order not to destroy the whole system a defined procedure of switching the 4 devices of a branch in a 3-level system has to be followed. Even more critical is switching in a 5 level system. However, the higher-level systems require less magnetically decoupled transformers.

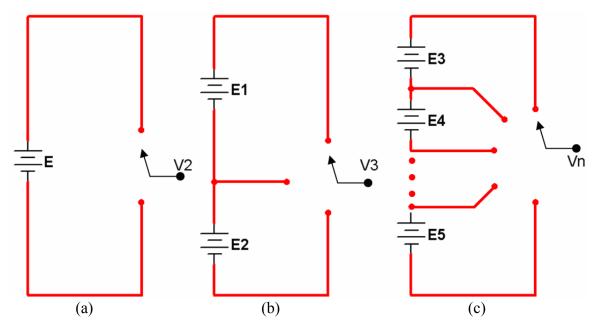

Figure 2-5: Inverter legs a) 2-level inverter, b) 3-level inverter, c) n-level inverter

## 2.3 Three-Phase Two-Level H-Bridge Topology

# 2.3.1 Configuration of Circuit

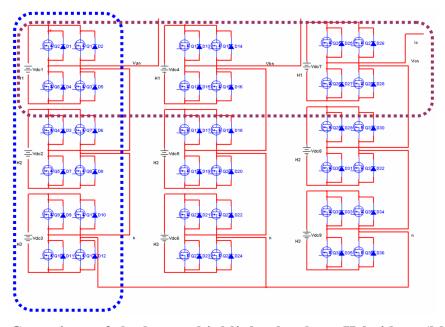

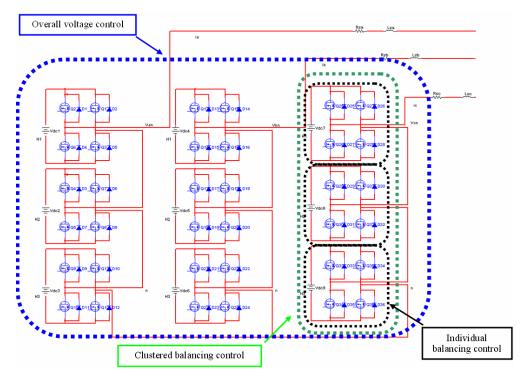

Figure 2-6: Groupings of the legs to highlight the three H-bridges (blue lines) or the two 3-phase inverters (brown lines)

Figure 2-7: A Y-connection, seven-level cascaded converter connected to the power system

Three-phase 2L-H-Bridge, represented in figure 2-7, which was implemented mostly in systems, has separate DC sources [13][42]. The main issue is to balance the voltage of DC busses keeping the power distribution equally.

This class of multi-level converters is based on a series connection of single-phase converters and power conversion cells where the voltage and power level may be easily scaled. Most of the researches on multilevel inverter types are concentrated in diode-clamped, flying capacitor and cascade inverter groups.

Multilevel converters offer a better output power quality of the output waveforms than standard converters. The dc link supply for each H-bridge converter element must be provided separately. The ability to synthesize higher number of output voltage levels with a sufficient harmonic spectrum utilizing power semiconductors and capacitors are important advantages of this topology. However, the large number of power devices and of voltages required to supply each cell with a complex and expensive isolating transformer, as well as control the complexity are drawbacks.

The SC2LHB VSCs will be designated according to the voltage levels of the individual H-bridge cells. The step of the output voltage is comparatively small and equal to the dc bus voltage of H-bridge cell. To attain the rated medium output voltage, all single-phase low-voltage H-bridge cells are connected over the secondary sides of transformers in series, using low-cost low-voltage devices.

Table 2-2 Simulation parameters

| Cascade number, N               | 3                   |

|---------------------------------|---------------------|

| Voltage line-to-neutral         | 7                   |

| Voltage line-to-line            | 13                  |

| DC Voltage                      | 30V                 |

| Reference wave frequency, $f_m$ | 50Hz                |

| Carrier wave frequency, $f_s$   | 4, 8, 10 and 20 kHz |

| Number of MOSFETs               | 36                  |

Table 2-2 shows the total required components of two investigated multi-level converters as a function of the number of voltage levels. Although the same number of modules (MOSFETs/diodes) is needed in the considered topologies, the total number of components necessary in these topologies is different at higher voltage levels. In the same voltage range, the NPC requires substantially more components than the others do; therefore, it does not qualify for the use with a high number of voltage levels. Moreover, for more than three-level configuration, the NPC voltage imbalance problem cannot be overcome by utilizing modulation techniques [25][103]. Complex balance circuits would be necessary. This makes the NPC unattractive for levels larger than three.

Table 2-3 Comparison of power component requirements for multi-level topologies

|                           | Series Connected 2-Level H-Bridge (transformers at the input of inverter which is potentially separated with DC input) | Series Connected 2-Level H-Bridge (transformers at the output of inverter) |

|---------------------------|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| Number of modules         |                                                                                                                        |                                                                            |

| (MOSFET/Diode)            | 6(N-1)                                                                                                                 | 6(N-1)                                                                     |

| Number of clamping diodes | 0                                                                                                                      | 0                                                                          |

| Number of dc link         |                                                                                                                        |                                                                            |

| capacitors                | 3(N-1)/2                                                                                                               | 3(N-1)/6                                                                   |

| Number of balancing       |                                                                                                                        |                                                                            |

| capacitors                | 0                                                                                                                      | 0                                                                          |

| Total                     | 15(N-1)/2                                                                                                              | 15(N-1)/6                                                                  |

Table 2-4 Comparison of 5L SC2LHB-VSC regarding to IGBTs and MOSFETs

|                             | 5L SC2LHB-VSC  |                |                |                |  |  |  |  |

|-----------------------------|----------------|----------------|----------------|----------------|--|--|--|--|

|                             | IGB'           | Γ              | MOSFET         |                |  |  |  |  |

|                             | APOD           | NEW            | APOD           | NEW            |  |  |  |  |

|                             | $f_s = 1050Hz$ | $f_s = 1050Hz$ | $f_s = 1050Hz$ | $f_s = 1050Hz$ |  |  |  |  |

|                             | m=0.9          | m=1            | m=0.9          | m=1            |  |  |  |  |

|                             | %              | %              | %              | %              |  |  |  |  |

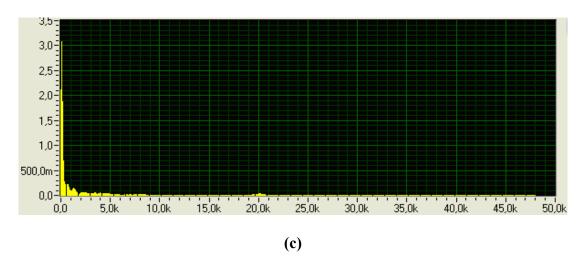

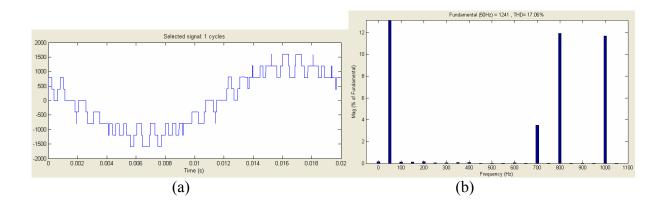

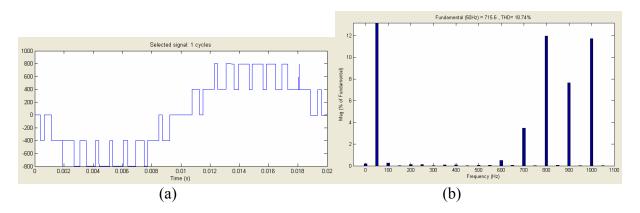

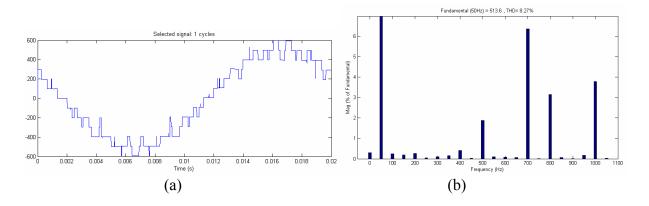

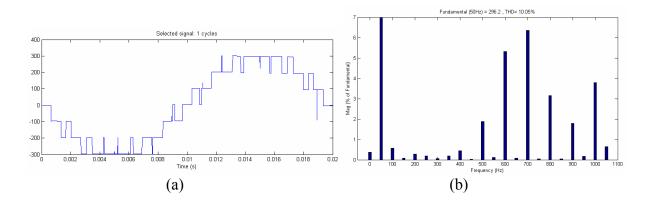

| V phase                     | 18.74          | 10.05          | 55.51          | 10.37          |  |  |  |  |

| $V_{\mathit{line-to-line}}$ | 17.06          | 8.27           | 40.96          | 8.29           |  |  |  |  |

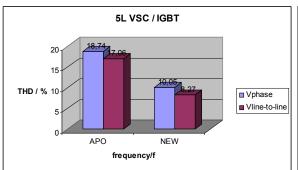

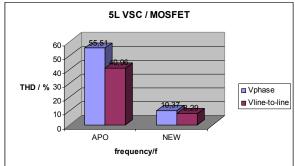

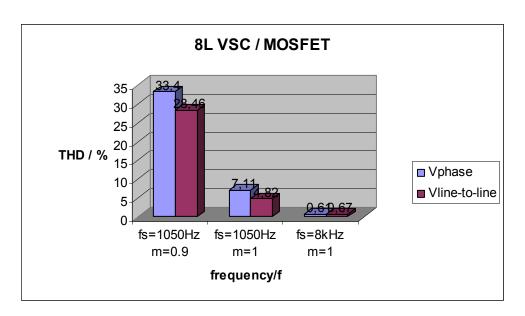

As shown in table 2-4 the comparison indicates that new method has better voltage outputs due to lower switching algorithm for a single-phase load.

Figure 2-8: THD comparison of 5L VSC (IGBT) and 5L VSC (MOSFET)

In figure 2-8, THD of  $V_{\it phase}$  and  $V_{\it line-to-line}$  shows a great difference between APOD method and our approach which has been simulated for IGBT and MOSFET configurations.

#### 3 Main New Contribution

A designer implements the application following a certain trajectory of design levels in a top-down approach, i.e. from algorithm level to circuit level, which can be defined as design flow [11][109][112][123]. Each design level includes large collection of low power techniques which may result into a significant reduction of the power consumption [64][77][90].

Figure 3-1: Design flow with power analysis/estimation steps [2][35]

Actually, this issue is an open research topic, strongly-depended on the application requirements [106]. The designer specifies the starting and final design level of a design

procedure, which may be a subset of a general top-down approach and therefore the use of optimization low power techniques and the estimation of the power loss must be performed [96]. To fully manage and optimize power consumption, a design flow must address power consumption issues at each stage of the design process and at each level of design abstraction. A top-down approach is illustrated in figure 3-1, which summarises the flow of steps that are required to go from a system-level specification to circuit level analysis.

As we have seen, the design for low power starts with a target specification, selecting the right algorithm and optimizing the behavioural description of the algorithm using transformation. If that description meets the specification we transform the behavioural description into a structural implementation.

#### 3.1 Quasi-Eight-Level Inverter

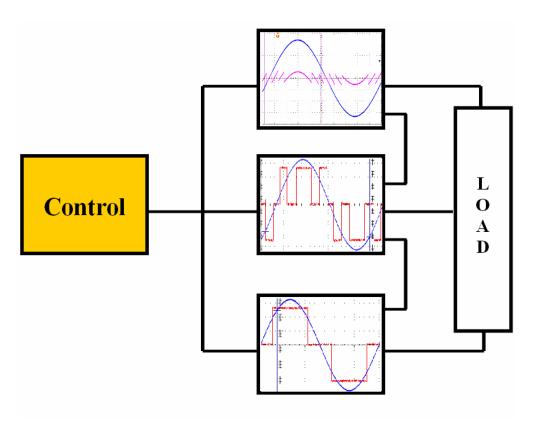

The actual system will be composed of inverters which run at the same DC-link voltage and should include same type of switches for standardization purposes. We select a simple control set based on the standard triangle wave-sinusoidal reference comparison to get switching states. Alternate Phase Opposition Disposition (APODPWM) technique is employed in simulation phase to control the switching devices of the first voltage-source inverter and as well as for the rest of the inverters.

Figure 3-2: Control the separated inverters

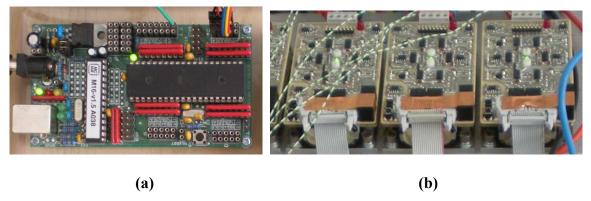

For the proposed harmonic reduction technique, the theoretical analysis of 1-2-4 stepped voltage inverter is presented. By using a systematic method, only the polarities and the number of levels are required to be determined for different modulation levels [32][78]. Computer simulation results are provided. To verify the theory and the simulation results, a

cascade inverter based hardware prototype including a low cost 8-bit microcontroller and modularized power stage and gate driver circuits, is implemented. Experimental results indicate that the proposed technique is effective for harmonic reduction in multilevel converters, and that both theoretical and simulation results are well validated.

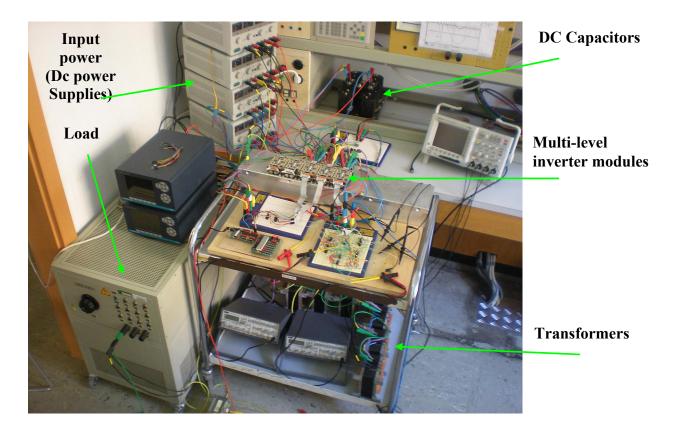

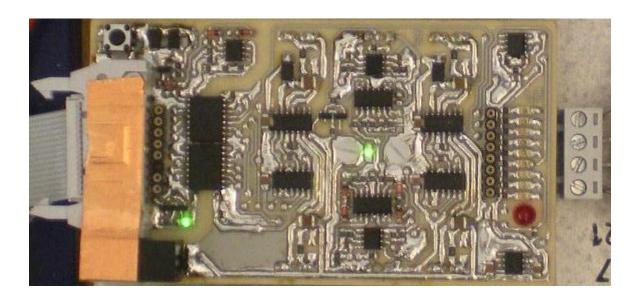

In a power stage, four MOSFET, SPP20N60C3 model, are used as the main switches, which are connected in full-bridge configuration. After the test on the reduced scale converter, some test benches were implemented. The SPWM and the power sharing capability were tested. Computer simulation results are provided in chapter 6.

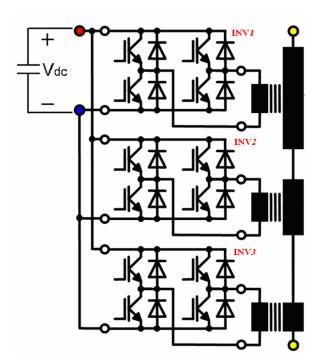

A single-phase H-bridge inverter, as shown in figure 3-3, supplies a resistance from a DC source [36][37]. Inverter 1 has power transfer value  $S_0$ . Therefore, inverter 2 shall have double that power transfer value, i.e.  $2*S_0$ . As a rule of thumb, a standard design for industrial systems exhibits switching losses in controlled semiconductors being equal on-state losses.

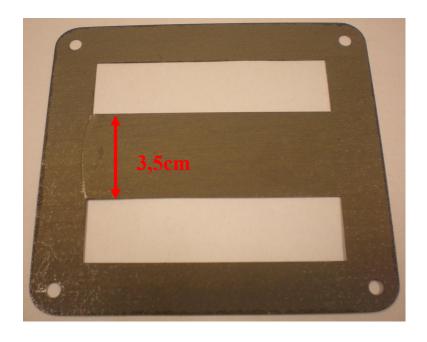

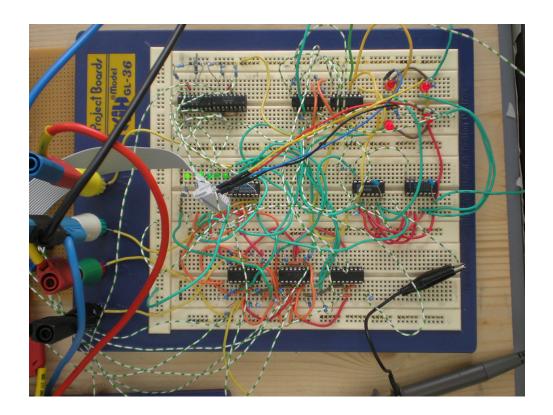

Figure 3-3: Laboratory model hardware layout

For a really good output voltage quality, we will choose a slightly higher frequency than this. Then we can estimate that inverter 2 can be exactly the same device as inverter 1. Inverter 2 runs at 3 times the fundamental frequency and the corresponding switching losses practically can be neglected for IGBT and MOSFET devices of intended power ranges whereas inverter 3 runs with the fundamental frequency. This allows about 2 times current capability which yields the demanded value of  $2*S_0$  for inverter 2. The whole system requires 3 identical 2-level standard single-phase inverters only.

For practical evaluation of total system we establish a laboratory model. For cost reasons, we also integrate used components as transformers. We have 7 identical transformers organized in parallel groups of 1, 2, and 4. We also use 7 identical inverters implementing MOSFET switches for the laboratory model.

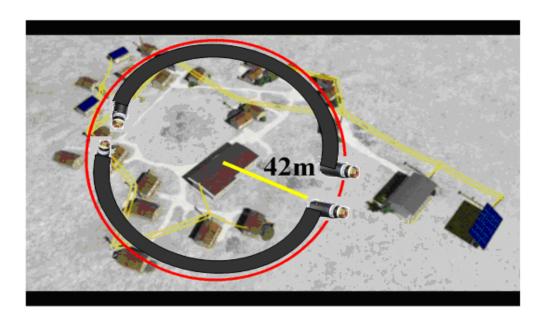

This doctoral thesis includes discussions and research assignments of system design, describes the development of a stand-alone wind turbine. Various possible configurations are investigated and a configuration using a multi-level inverter is chosen. A model is developed for controller design of the fast controllers of the system and a prototype is built for testing. The documents the performance of the prototype through measurements done on a prototype installed in a test facility where it has been tested both as a standalone unit and in parallel with battery test equipment are reported. For system wide power quality assessment and controller design a dynamic performance assessment model has been developed. As a case study, specific large wind turbine is used, and the concept is applicable for any type of wind turbine.

## 3.2 Comparison to Conventional Systems

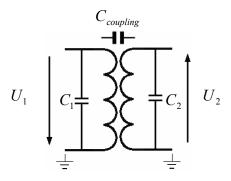

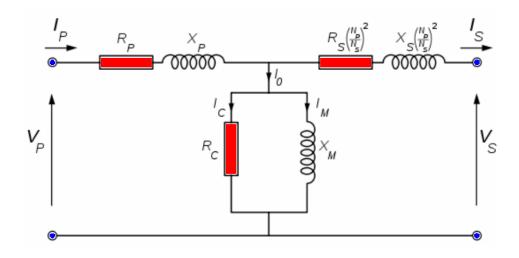

Our new contribution has advantages compared to other standard multilevel inverter topologies. Common inverter approaches have isolation transformers with delta, star, or zigzag winding connections. The most complex part is to determine the needed parameters such as inductance and resistance values of each transformer. In this thesis, all the inverters are fed by a common DC bus. The transformers are located at the output side of the inverters which the primary sides are connected to each inverter in parallel and the secondary sides are connected in series. Grouping of these seven transformers as 1, 2 and 4, total 7 voltage levels can be produced. Referring to sinus voltage, each group of transformer acts differently in one period. Therefore, switching states of these three groups of transformers determine the total harmonic distortion and losses of the inverters. Switching frequencies between 4 kHz...20 kHz, are the main operation area of the MOSFETs inverter and experimental results show better output voltage with the increasing frequencies.

These advantages prevent filter implementation which is usually a common solution and also decrease the costs in such kind of systems.

# 4 Modelling of Quasi-Eight-Level Inverter

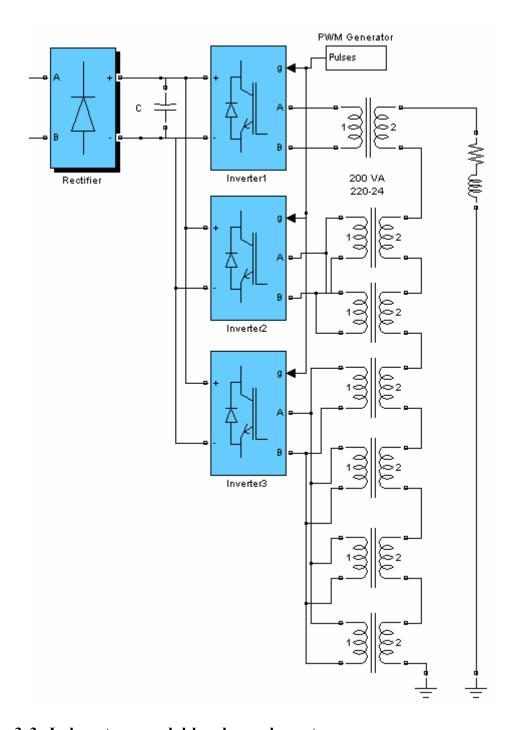

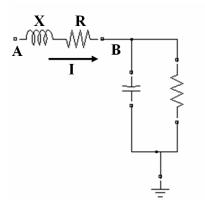

The circuit of figure 4-1 shows the basic topology of an H-bridge converter used for the implementation of SC2LHB VSCs. It is based on the simple, four switches converter, which is usually used for single-phase applications. A three-phase diode rectifier charges the dc capacitor and the dc voltage feeds a single-phase MOSFET bridge, which generates the PWM output of the power cell. In order to simplify the system and yet yield high output voltage quality without excessive individually operated switches and without extensive filtering we propose the quasi-8-level converter circuitry including the adapted output transformer that was shown in chapter three.

Figure 4-1: Typical power cell (H-bridge) converter

The parameters used in simulation for H-bridge converter are as follows and detailed configuration can be seen in appendix A.

**Table 4-1 Simulation parameters**

| DC Voltage, E                   | 30V                 |

|---------------------------------|---------------------|

| Modulation index, $M_a$         | 0.9                 |

| Reference wave frequency, $f_m$ | 50 Hz               |

| Carrier wave frequency, $f_s$   | 4, 8, 10 and 20 kHz |

| Snubber resistance, $R_s$       | 100Ω                |

| Snubber capacity, $C_s$         | 220 <i>nF</i>       |

| Load resistance, R              | 15Ω                 |

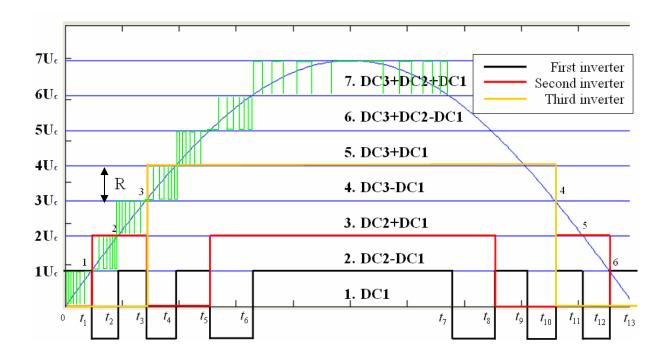

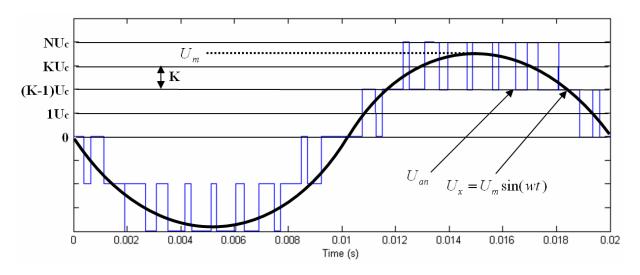

Figure 4-2: Quasi eight-level inverter and output-voltage generation

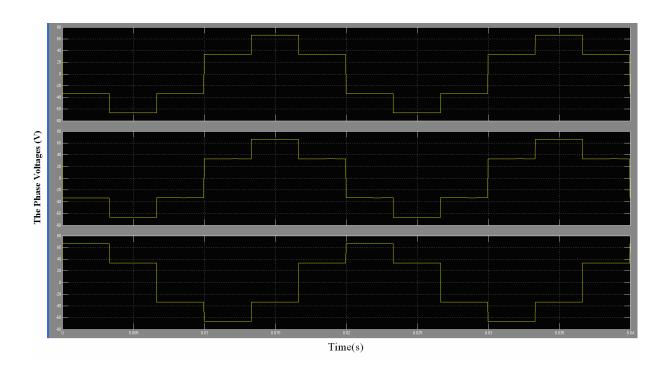

Figure 4-2 shows a half period of one cycling. The first inverter which is being controlled as PWM method helps as an auxiliary converter partially switches in "+" or "-" direction in order to produce stepped level voltages. The second and third inverters are the main blocks of the sinusoid signal and therefore are switched on or off extremely rarely compared to the first inverter. By this way, conduction and switching losses can be reduced.

Table 4-2 Switching conditions of each inverter

|                       | 1. Inverter (in PWM mode) | 2. Inverter | 3. Inverter |

|-----------------------|---------------------------|-------------|-------------|

| $0 < t < t_1$         | +1                        | 0           | 0           |

| $t_1 < t < t_2$       | -1                        | +1          | 0           |

| $t_2 < t < t_3$       | +1                        | +1          | 0           |

| $t_3 < t < t_4$       | -1                        | 0           | +1          |

| $t_4 < t < t_5$       | +1                        | 0           | +1          |

| $t_5 < t < t_6$       | -1                        | +1          | +1          |

| $t_6 < t < t_7$       | +1                        | +1          | +1          |

| $t_7 < t < t_8$       | -1                        | +1          | +1          |

| $t_8 < t < t_9$       | +1                        | 0           | +1          |

| $t_9 < t < t_{10}$    | -1                        | 0           | +1          |

| $t_{10} < t < t_{11}$ | +1                        | +1          | 0           |

| $t_{11} < t < t_{12}$ | -1                        | +1          | 0           |

| $t_{12} < t < t_{13}$ | +1                        | 0           | 0           |

where "+1" denotes the upper direction, "-1" the reverse direction and "0" the no switching mode. To perform the above rules, the digital controller employs a flowchart. The digital controller takes the voltage samples and compares them with constant DC references. Then, the region of input voltage, R, is updated, the control algorithm is performed, and the appropriate switching functions are determined. The switching functions are applied to the H-bridge cells and the corresponding operating modes are selected by the multiplexers. This procedure is repeated in the next sampling periods.

The following remarks about this method should be noted:

- In the proposed controller, there are two modulation mechanisms. One is generated by the analogue controller, termed as PWM mode, and the other is done by the digital controller, termed as low switching voltage algorithm.

- During each sampling period, the switching functions do not change.

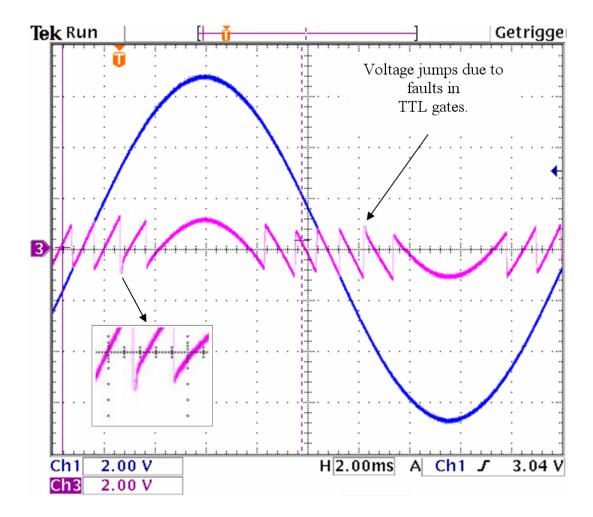

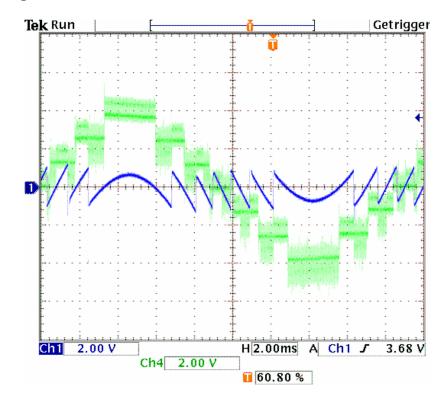

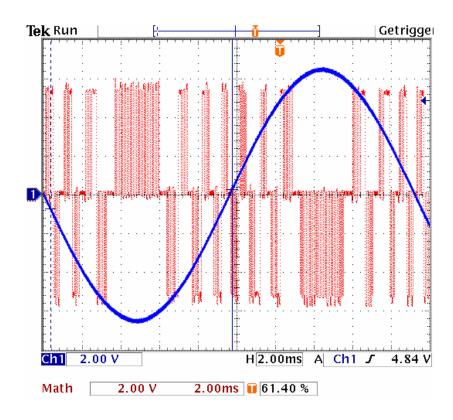

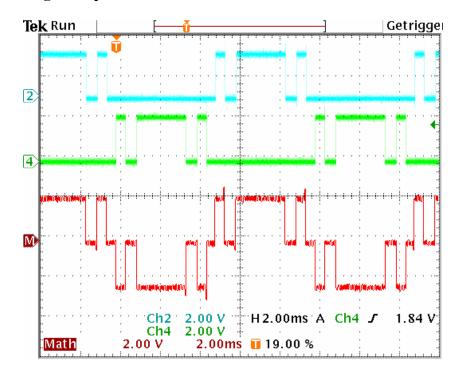

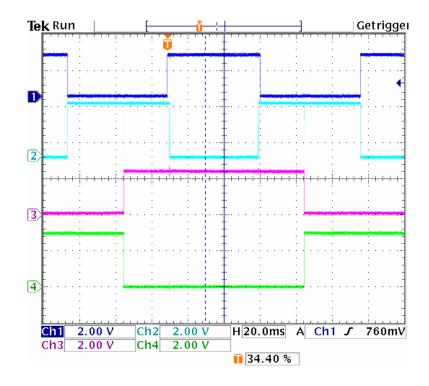

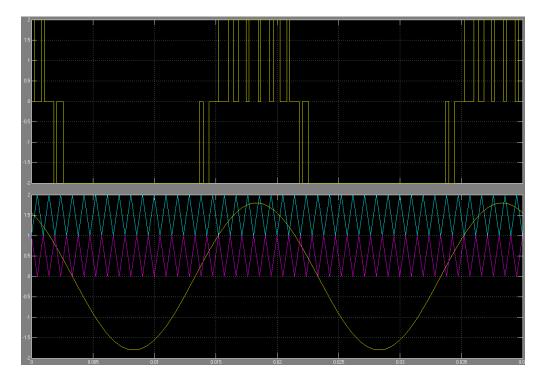

Figure 4-3: PWM controlled signal (pink)

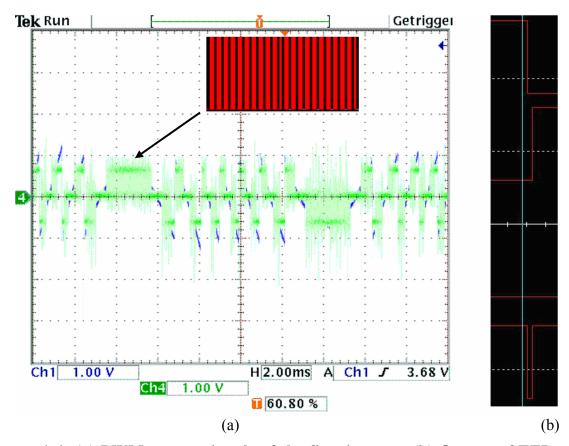

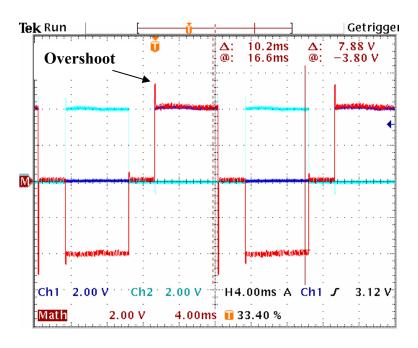

In figure 4-3, pink-coloured signal is gained from the reference sinus signal for PWM control and is compared with carrier waveforms. As seen in figure 4-4 (b), there is time interval between the gates. Logic gates operate in nanoseconds (20 ns), and each TTL gate needs time interval in order to switch on or off. This problem causes delays and voltage fluctuations.

Figure 4-4: (a) PWM output signals of the first inverter (b) Output of TTL gates

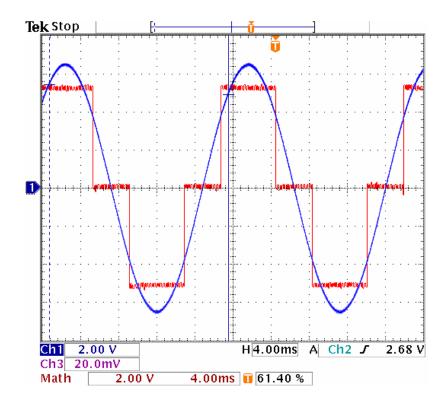

Figure 4-5: Output signal of the inverter

Figure 4-6: PWM signals of the first inverter

Only first inverter cell is modulated by a sine-triangle modulation as shown in figure 4-5. Practically, these signals are then modulated with sinusoid signal which is shown in figure 4-6 (blue line).

#### 4.1 Modulation Method

#### 4.1.1 Sine-Triangle Modulation

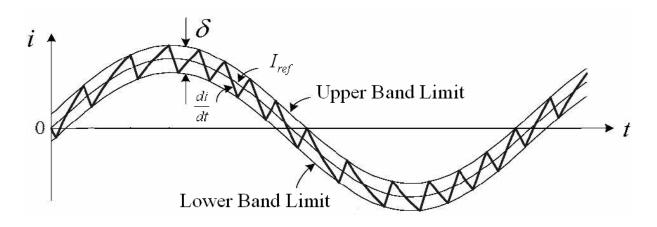

One first impression of a multilevel power converter is that the large number of switches may lead to complex pulse-width modulation (PWM) switching algorithms and requires many driving circuits [19][20]. However, early developments in this area demonstrated the relatively straightforward nature of multilevel PWM [22]. The purpose of PWM single-phase converter is to shape and to control the single-phase output voltage in magnitude and frequency with a practically constant input voltage  $U_{dc}$  [31]. To obtain single-phase output voltage in a single-phase PWM, the same triangular voltage waveform  $U_{C1}$  and  $U_{C2}$  are compared with control voltage waveform  $(U_{\sin})$ .

The frequency modulation ratio  $m_f$  and the amplitude modulation ratio  $M_a$  of a PWM are defined as

$$m_f = \frac{f_C}{f_m} \tag{4-1}$$

In order to eliminate even harmonics, the frequency modulation ratio  $m_f$  should be odd. The odd harmonics in the phase-midpoint voltages are the same as the output of any one of the legs, centred on the switching frequency and its multiples  $(m_f, 2m_f ...)$ .

$$M_a = \frac{U_R}{U_{C_1}},\tag{4-2}$$

where  $U_{\it R}$  denotes the peak value of the fundamental component of the reference voltage. For a sine-triangle modulation of three-phase inverter the linear modulation range is limited to values of

$$0 \le M_a \le \frac{2}{\sqrt{3}} \tag{4-3}$$

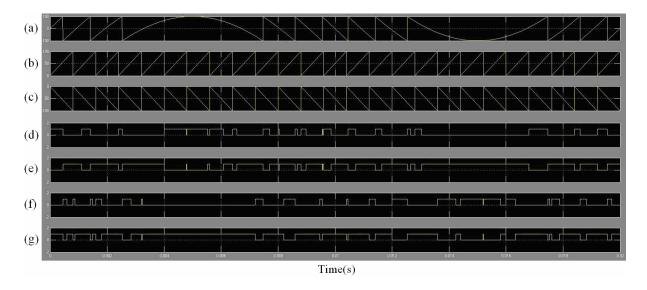

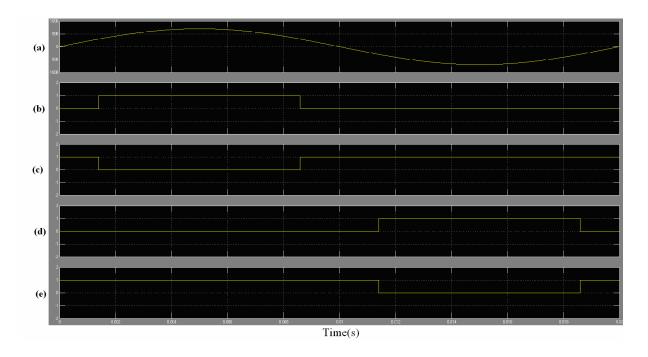

Figure 4-7: PWM control of proposed inverter (first inverter) (a) sinusoidal signal, (b) upper triangular signal, Uc1 (c) lower triangular signal, Uc2 (d) positive portion of Ton,1, (e) negative portion of Ton,2 inverted, (f) positive portion of Ton,3, (g) negative portion of Ton,4 inverted

In order to generate the switching signals, two triangular voltage waveforms  $U_{\rm C1}$  and  $U_{\rm C2}$ , as shown in figure 4-7, are determined by the comparison of the corresponding carrier signal and the reference signal  $U_{\rm R}$ . Thus, there are four commutations during one period of the carrier signal. As shown in figure 4-8, the comparison of  $U_{\rm R}$  with  $U_{\rm c1}$  and  $U_{\rm c2}$  results in the following logic signals to control the switches in the first leg.

$$U_{an} = \begin{cases} U_{dc} & where U_{R} > U_{c1} (Q_{2}, Q_{3} : ON, Q_{1}, Q_{4} : OFF) \\ 0 & where U_{R} < U_{c1} (Q_{1}, Q_{2} : OFF, Q_{3}, Q_{4} : ON) \end{cases}$$

(4-4)

For controlling the second leg switches,  $U_{C2}$  is compared with the same control signal, which yields following

$$U_{an} = \begin{cases} 0 & where U_{R} > U_{c2} (Q_{1}, Q_{2} : OFF, Q_{3}, Q_{4} : ON) \\ (-U_{dc}) & where U_{R} < U_{c2} (Q_{1}, Q_{4} : ON, Q_{2}, Q_{3} : OFF) \end{cases}$$

(4-5)

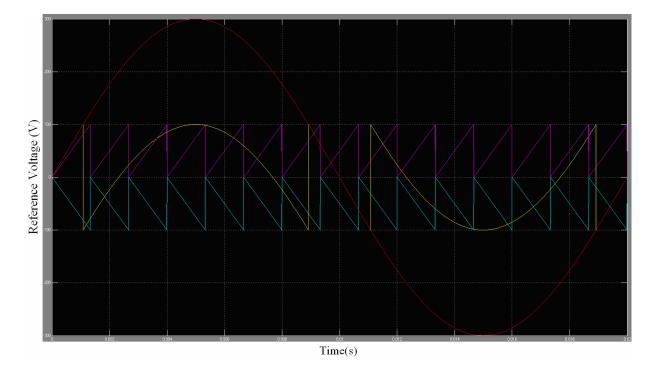

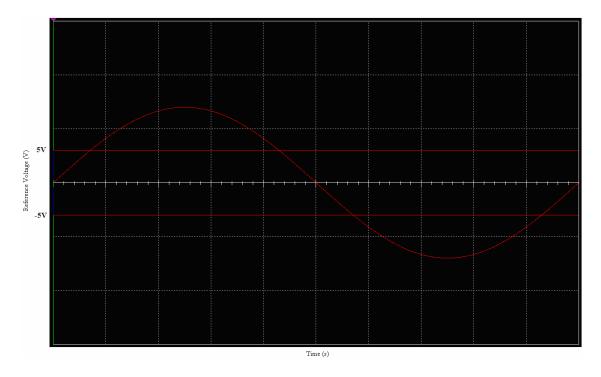

Figure 4-8: PWM control of the first inverter (sine-triangle intersection)

Yellow line shows the signal that will be pulse modulated using PC849 high density mounting type photo coupler. This signal is the subtraction of signals from reference input which are currents derived from a constant 12V DC supply over  $1\,k\Omega$ ,  $3\,k\Omega$  and  $6\,k\Omega$  resistances. Comparing the reference signals with sinusoid, the PC849 photo couplers switches ON or OFF and by the way the necessary current signals are derived and provided to TL084ACD.

Figure 4-9: Logic circuit of the third inverter

Each reference voltage is compared with sinusoidal signal and the states of the MOSFET gates are determined. Depending on the signal value, the reference voltage is compared with triangular carriers at each time.

Table 4-3 Logic map of the PWM signals

| (0)                       | (+)                       | (-)                               |

|---------------------------|---------------------------|-----------------------------------|

| (A <b>▼</b> C)▲B          | ٦                         | ( <b>A</b> ▼ <b>C</b> )▲ <b>B</b> |

| (A▼C)▼B                   | (A▼C)▼B 7                 |                                   |

|                           |                           |                                   |

| (A <b>▼</b> B) <b>▲</b> C | (A <b>▼</b> B) <b>▲</b> C | ¬ (A <b>▼</b> B) <b>▲</b> C       |

| (A <b>▼</b> B) <b>▼</b> C | ( <b>A▼</b> B) <b>▼</b> C | ¬(A <b>▼</b> B) <b>▼</b> C        |

where " $\nabla$ " denotes "OR", " $\triangle$ " denotes "AND" and " $\gamma$ " denotes "NOT". The logical outputs are determined with the changing states and drive the inverter correctly. "A", "B" and "C" are the output signals for computing the (+), (-) and (0) states.

Table 4-4 States of each MOSFETs of the PWM signals

|              | Q2  | Q1  |

|--------------|-----|-----|

| В            | ON  | OFF |

|              | Q4  | Q3  |

| Plus(+)      | OFF | ON  |

|              | Q2  | Q1  |

| A            | OFF | OFF |

|              | Q4  | Q3  |

| Zero (0)     | ON  | ON  |

|              | Q2  | Q1  |

| C            | OFF | ON  |

|              | Q4  | Q3  |

| Negative (-) | ON  | OFF |

Figure 4-10: Typical power cell (H-bridge) converter

The use of PWM voltage switching causes a smaller ripple on the dc current side [53]. We notice that when both the lower or upper switches are "ON", the output voltage is zero. The output current circulates in a loop through (Q2, D1) or (D2, Q1), depending on the direction of  $i_{ph}$ . During this interval, the current  $i_{dc}$  is zero. A similar condition occurs when both bottom switches Q4 and Q3 are turned on.

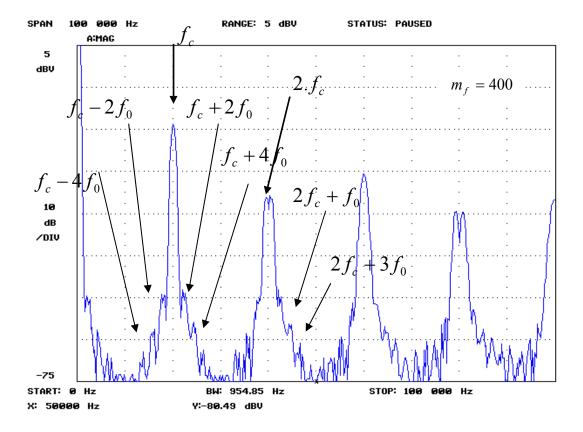

Because of the diodes in anti-parallel with the switches, the foregoing voltage is independent of the direction of the output current  $i_{ph}$ . Two legs of the H-bridge are controlled separately, the first carrier band harmonics of the output voltage occur at twice the corresponding carrier frequency (ficb = 2fc) [39]. This advantage appears in the harmonic spectrum of the output voltage waveform, as shown in figure 4-25. If we choose the frequency modulation ratio  $m_f$  to be even, the output voltage waveforms of any one of the legs  $U_{ag}$  and  $U_{n/g}$  are displaced

by  $180^{\circ}$  of the fundamental frequency, with respect to each other. Therefore, the harmonic components at the switching frequency in any one of the legs have the same phase, since the output voltage waveforms are  $180^{\circ}$  displaced and  $m_f$  is assumed to be even. This results in the cancellation of the harmonic component at the sidebands of the switching frequency in the output voltage.

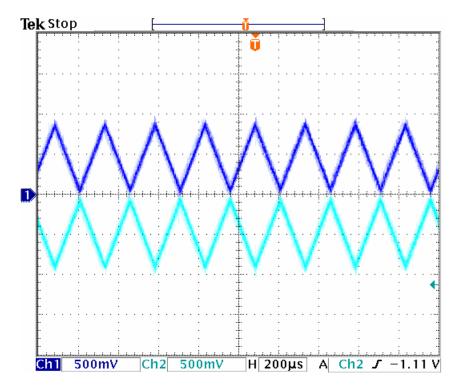

Figure 4-11: Carrier triangular waves

This PWM method uses two carrier signals of the same amplitude and frequency, which are inversed referring to point "0" with respect to each other which is another way to achieve multilevel modulation, one associated to the upper leg and another one associated to the lower leg. Figure 4-11 shows how two carriers are disposed. The upper leg carrier is a triangular wave sweeping from 0 to 1, while the lower leg carrier goes from 0 to -1. Setting the function generator  $V_{p-p}$ =0.75 V and  $V_{off-set}$ =0.37 V, the amplitude of signals are adjusted to 1V and -1V having different modulation index values ( $m_a$ ). In this way, only one leg commutates at one time and the total output is given by the overall effects of both legs. With the representation of figure 4-11, the output is obtained as the sum of the single leg outputs, so the gating signals of the lower leg must be neglected to achieve which is still valid.

Figure 4-12: Carrier triangular waves with respect to reference sinus signal

The switching points are determined by the intersection of the triangular carrier wave  $U_{c1}$  and  $U_{c2}$  which were controlled with different frequencies and amplitude and the reference modulation sine wave,  $f_0$  shown in figure 4-12. The output frequency is at the sine-wave frequency  $f_0$  and the output voltage is proportional to the magnitude of the sine wave.

Table 4-5 explains basic switching strategy to develop the seven steps yielding 8 levels (including level 0). The push-pull configuration again yields 7 positive steps and 7 negative steps. In a given band of voltage we use certain output voltages of defined inverters and add these voltages at defined transfer ratio of transformer over the series connection of output side windings.

The total number of switch states for the 8L-SC2LHB VSC is 36, and the voltage steps are 15 which breaks down to seven for the positive voltage, seven for the negative voltage, and one for the zero voltage.

Table 4-5 Quasi eight-level VSC switching states

|                         | Module1   |           |      | Modul     | le2       | Module3 |           |           |      |

|-------------------------|-----------|-----------|------|-----------|-----------|---------|-----------|-----------|------|

|                         | $T_{on1}$ | $T_{on2}$ | Vdc  | $T_{on1}$ | $T_{on2}$ | Vdc     | $T_{on1}$ | $T_{on2}$ | Vdc  |

| $Inv_3 + Inv_2 + Inv_1$ | 1         | 0         | Vdc  | 1         | 0         | Vdc     | 1         | 0         | Vdc  |

| $Inv_3 + Inv_2 - Inv_1$ | 0         | 1         | -Vdc | 1         | 0         | Vdc     | 1         | 0         | Vdc  |

| $Inv_3 + Inv_1$         | 1         | 0         | Vdc  | 1         | 1         | 0       | 1         | 0         | Vdc  |

| $Inv_3 + Inv_1$         | 1         | 0         | Vdc  | 0         | 0         | 0       | 1         | 0         | Vdc  |

| $Inv_3$ - $Inv_1$       | 0         | 1         | -Vdc | 1         | 1         | 0       | 1         | 0         | Vdc  |

| $Inv_3$ -v $INV_1$      | 0         | 1         | -Vdc | 0         | 0         | 0       | 1         | 0         | Vdc  |

| $Inv_2 + Inv_1$         | 1         | 0         | Vdc  | 1         | 0         | Vdc     | 1         | 1         | 0    |

| $Inv_2 + Inv_1$         | 1         | 0         | Vdc  | 1         | 0         | Vdc     | 0         | 0         | 0    |

| $Inv_2 - Inv_1$         | 0         | 1         | -Vdc | 1         | 0         | Vdc     | 0         | 0         | 0    |

| $Inv_2$ - $Inv_1$       | 0         | 1         | -Vdc | 1         | 0         | Vdc     | 1         | 1         | 0    |

| $Inv_1$                 | 1         | 0         | Vdc  | 0         | 0         | 0       | 0         | 0         | 0    |

| $Inv_1$                 | 1         | 0         | Vdc  | 0         | 0         | 0       | 1         | 1         | 0    |

| $Inv_1$                 | 1         | 0         | Vdc  | 1         | 1         | 0       | 0         | 0         | 0    |

| $Inv_1$                 | 1         | 0         | Vdc  | 1         | 1         | 0       | 1         | 1         | 0    |

| 0                       | 0         | 0         | 0    | 0         | 0         | 0       | 0         | 0         | 0    |

| 0                       | 0         | 0         | 0    | 0         | 0         | 0       | 1         | 1         | 0    |

| 0                       | 0         | 0         | 0    | 1         | 1         | 0       | 0         | 0         | 0    |

| 0                       | 0         | 0         | 0    | 1         | 1         | 0       | 1         | 1         | 0    |

| 0                       | 1         | 1         | 0    | 0         | 0         | 0       | 0         | 0         | 0    |

| 0                       | 1         | 1         | 0    | 0         | 0         | 0       | 0         | 0         | 0    |

| 0                       | 1         | 1         | 0    | 1         | 1         | 0       | 1         | 1         | 0    |

| $Inv_1$                 | 0         | 1         | -Vdc | 1         | 1         | 0       | 1         | 1         | 0    |

| $Inv_1$                 | 0         | 1         | -Vdc | 1         | 1         | 0       | 0         | 0         | 0    |

| $Inv_1$                 | 0         | 1         | -Vdc | 0         | 0         | 0       | 1         | 1         | 0    |

| Inv <sub>1</sub>        | 0         | 1         | -Vdc | 0         | 0         | 0       | 0         | 0         | 0    |

| $Inv_2$ - $Inv_1$       | 1         | 0         | Vdc  | 0         | 1         | -Vdc    | 1         | 1         | 0    |

| $Inv_2$ - $Inv_1$       | 1         | 0         | Vdc  | 0         | 1         | -Vdc    | 0         | 0         | 0    |

| $Inv_2 + Inv_1$         | 0         | 1         | -Vdc | 0         | 1         | -Vdc    | 0         | 0         | 0    |

| $Inv_2 + Inv_1$         | 0         | 1         | -Vdc | 0         | 1         | -Vdc    | 1         | 1         | 0    |

| $Inv_3 - Inv_1$         | 1         | 0         | Vdc  | 0         | 0         | 0       | 0         | 1         | -Vdc |

| $Inv_3 - Inv_1$         | 1         | 0         | Vdc  | 1         | 1         | 0       | 0         | 1         | -Vdc |

| $Inv_3 + Inv_1$         | 0         | 1         | -Vdc | 0         | 0         | 0       | 0         | 1         | -Vdc |

| $Inv_3 + Inv_1$         | 0         | 1         | -Vdc | 1         | 1         | 0       | 0         | 1         | -Vdc |

| $Inv_3 + Inv_2 - Inv_1$ | 1         | 0         | Vdc  | 0         | 1         | -Vdc    | 0         | 1         | -Vdc |

| $Inv_3 + Inv_2 + Inv_1$ | 0         | 1         | -Vdc | 0         | 1         | -Vdc    | 0         | 1         | -Vdc |

To take advantage of both low frequency (stepped modulation) and high frequency (PWM) modulation techniques, we employ the both modulation method as shown in figure 4-13. In this method, the input voltage  $U_x$  is divided into equal sections with the scale of  $U_c(U_c)$  is the reference of DC-link voltages). Now we define the voltage region K as follows:

Region K:

$$(K-1)U_c < U_x < KU_c$$

,  $K = 1,..., N$

Region K is the voltage interval that the magnitude of input voltage,  $|U_x|$ , lies between  $(K-1)U_c$  and  $KU_c$ . Note that the minimum number of cells to synthesize the multilevel waveform,  $U_{an}$  is equal to the closest integer greater than  $(U_m/U_c)$ , where  $U_m$  is the peak input voltage.

Figure 4-13: Definition of voltage regions for K = 1,..., N

### 4.1.2 Discrete Implementation

It will be seen that the discrete method presented herein relies on computation directly from the duty cycles and therefore it is not necessary to define triangle waveforms or voltage vectors. For this reason, it is preferred to use microprocessors for the second and third inverter control algorithm while sine-triangle modulation is useful in that it can provide a straightforward method of describing multilevel modulation for the first inverter.

# 4.1.3 First Inverter

Figure 4-14: Carrier triangular waves with respect to reference sinus signal

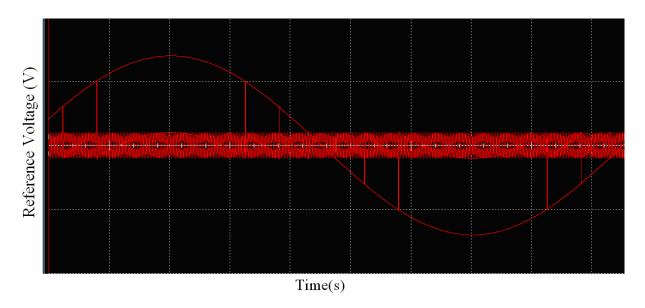

Figure 4-15: PWM signals of the first inverter (20 kHz). (a) positive portion of Ton, 1, (b) negative portion of Ton, 2 inverted, (c) positive portion of Ton, 3, (d) negative portion of Ton, 4 inverted

The first inverter generally runs at higher switching frequency for minimizing harmonics. We select a simple control set based on the standard triangle wave-sinusoidal reference comparison

to get switching states. Then we perform a Fourier analysis of idealized total output voltage at the transformer.

#### 4.1.4 Second Inverter

For low-switching-frequency applications, low switching voltage algorithm is used. The basic idea of this technique is to connect each cell of the inverter at specific angles to generate the multilevel output waveform, producing only a minimum of necessary commutations. Note that only one angle needs to be determined per power cell. These angles can be computed using the principle

$$U_R = U \sin(\omega t) \tag{4-6}$$

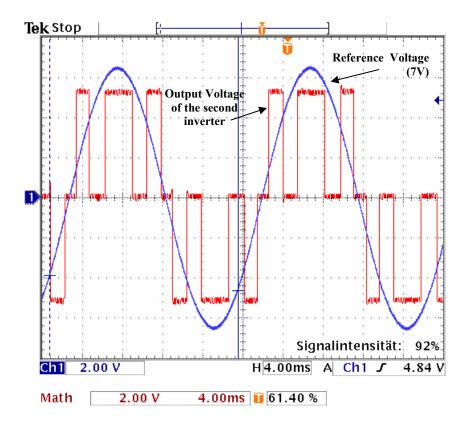

Figure 4-16: Constant DC voltages compared to reference sinus signal of the second inverter

Figure 4-17: Illustration of the second inverter output respect with reference sinus signal

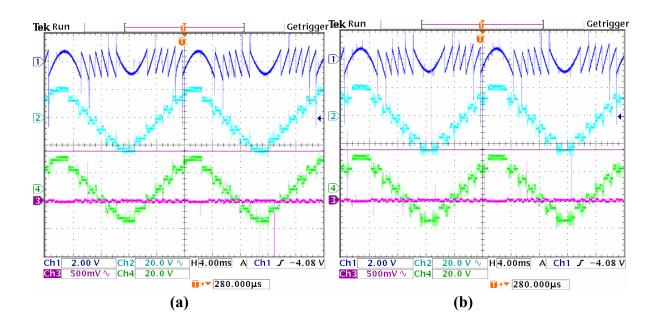

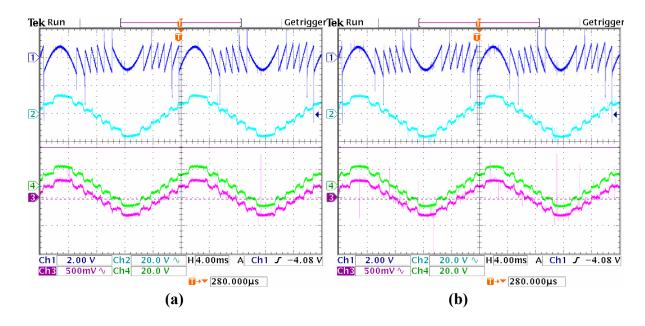

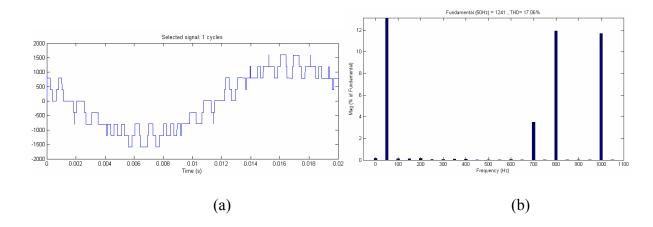

The second inverter is seen in figure 4-17 shows the switching times during two periods. The reference voltage values are -1V, -3V, -5V, 1V, 3V and 5V.

$$Inverter_{2} = \begin{cases} ON & (3V > U_{R} > 1V) or(U_{R} > 5V) or(-1V > U_{R} > -3V) or(-5V > U_{R} \\ OFF & (1V > U_{R} > -1V) or(5V > U_{R} > 3V) or(-5V > U_{R} > -3V) \end{cases}$$

(4-7)

where  $U_R$  is sinus signal. Decreasing the losses is done with low switching frequencies, namely 6 times ON, 6 times OFF.

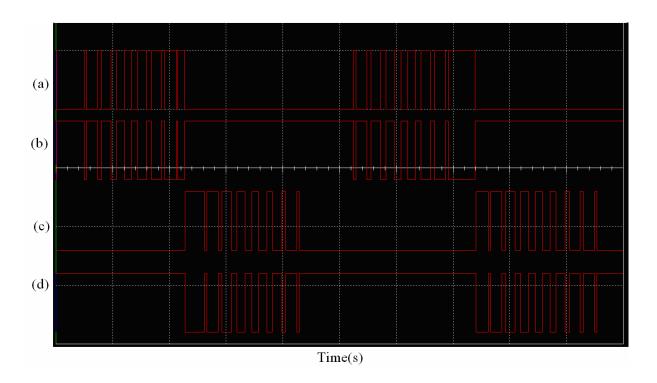

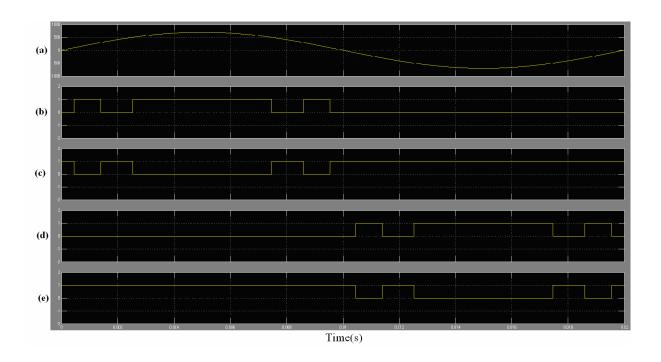

Figure 4-18: PWM control of proposed inverter (second inverter) (a) sinusoidal signal, (b) upper triangular signal, Uc1(c) lower triangular signal, Uc2 (d) positive portion of Ton,1, (e) negative portion of Ton,2 inverted, (f) positive portion of Ton,3, (g) negative portion of Ton,4 inverted

Figure 4-19: Illustration of the control signals of the second inverter

# 4.1.5 Third Inverter

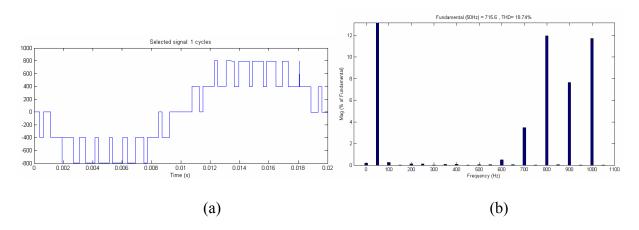

For the third inverter, the same principle is used to compute the angles.

Figure 4-20: Constant DC voltages compared to reference sinus signal of the third inverter

Figure 4-21: Illustration of the control signals of the third inverter

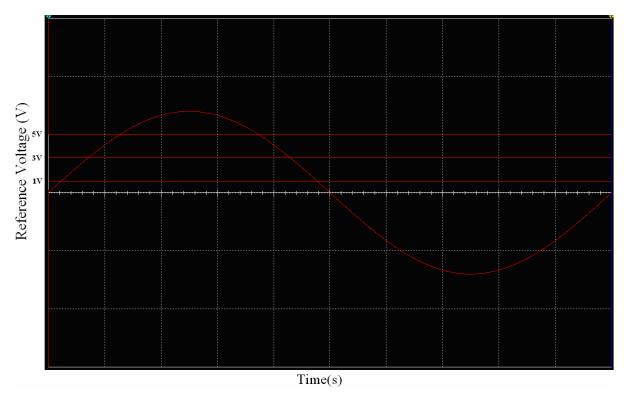

Figure 4-22: Illustration of the third inverter output respect with reference sinusoidal signal

The third inverter, seen in figure 4-22, shows the switching times during two periods. The reference voltage values are -5V, and 5V.

$$Inverter_{3} = \begin{cases} ON & U_{R} > (5V)or(-5V) > U_{R} \\ OFF & (5V) > U_{R} > (-5V) \end{cases}$$

$$(4-8)$$

The third inverter, seen in figure 4-23, shows the switching times during one period. Decreasing the losses is done with low switching frequencies, namely 2 times ON, 2 times OFF in one period. Compared to second inverter, the third inverter operates only at one third of switching frequency times and has less loss.

Figure 4-23: PWM control of proposed inverter (third inverter) (a) sinusoidal signal, (b) upper triangular signal, Uc1 (c) lower triangular signal, Uc2 (d) positive portion of Ton,1, (e) negative portion of Ton,2 inverted, (f) positive portion of Ton,3, (g) negative portion of Ton,4 inverted

The main advantage is that the converter very few times per cycle, reducing the switching losses to a minimum. In addition, low-order harmonics are eliminated, facilitating the output-filter design [75]. However, this method needs important off-line calculations to compute the angles for a variety of modulation indices and is therefore not very suited for highly dynamic systems.

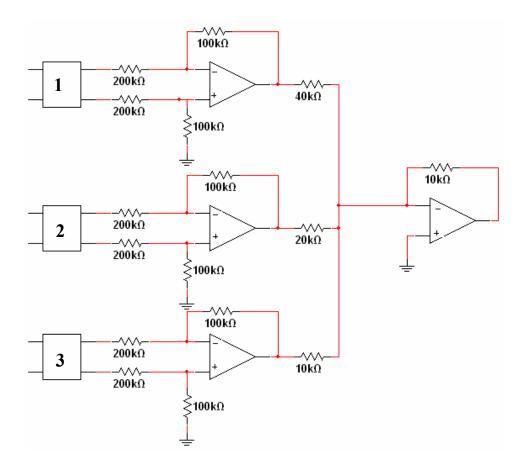

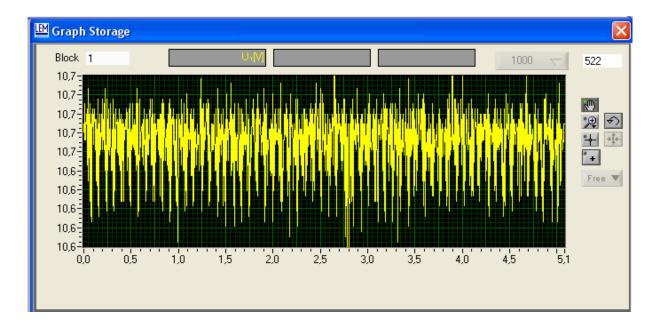

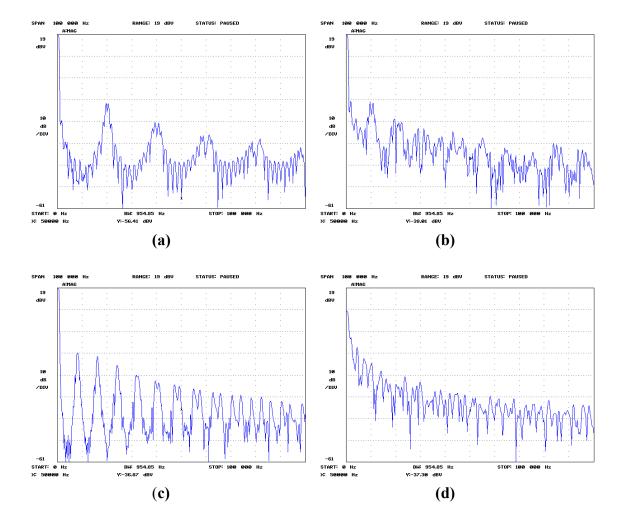

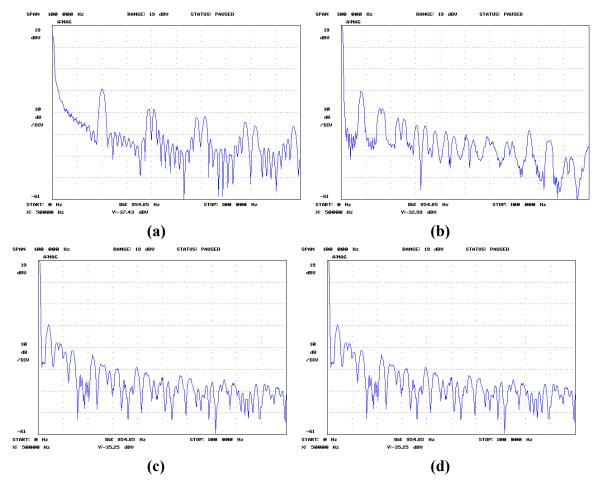

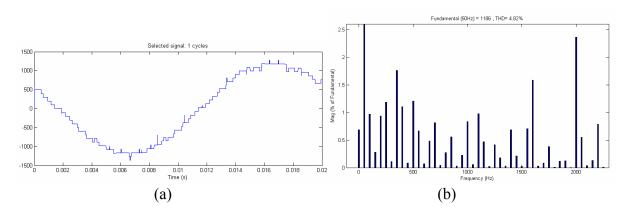

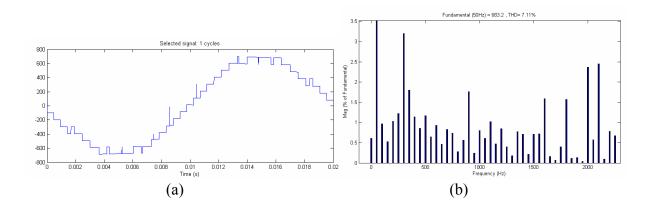

Figure 4-24: Harmonics measurement of three inverters via summing amplifiers

Total harmonic distortion is measured by amplifying and summing the output signals of each inverter [58]. The output than is given to Dynamic Signal Analyzer HP 3561A, connecting it to the computer and monitoring the signals as given in figure 4-24. Each of the inverter output is amplified and all added up in order to obtain the total harmonic components which is being measured by the signal analyzer.

Weighted total harmonic distortion (weighted THD) is proposed by Holmes [31] and is used in this chapter for the analysis and comparison of spectral performance of the different modulation techniques. Normalizing this expression to the quantity  $U_1/(\omega_1 L)$  the weighted total harmonic distortion (WTHD) becomes defined as

$$WTHD = \frac{\sqrt{\sum_{i=2}^{\infty} \left(\frac{U_i}{i}\right)^2}}{U_1}$$

(4-9)

where  $U_1$  is the fundamental voltage.

Table 4-6 shows the total required components of in two investigated multi-level converters as a function of the number of voltage levels. Although the same number of modules

(MOSFETs/diodes) is needed in the two considered topologies, the total number of components necessary in these two topologies is different at higher voltage levels.

Table 4-6 Comparison of power component requirements for multi-level topologies

| Topology            | Series Connected 2-Level H-Bridge (with different DC bus) | Series Connected 2-Level H-Bridge (with the same DC bus) |

|---------------------|-----------------------------------------------------------|----------------------------------------------------------|

| 1 03                | (with different DC bus)                                   | (with the same DC bus)                                   |

| Number of modules   |                                                           |                                                          |

| (MOSFET/Diode)      | 6(N-1)                                                    | 6(N-1)                                                   |

| Number of clamping  |                                                           |                                                          |

| diodes              | 0                                                         | 0                                                        |

| Number of dc link   |                                                           |                                                          |

| capacitors          | 3(N-1)/2                                                  | 1                                                        |

| Number of balancing |                                                           |                                                          |

| capacitors          | 0                                                         | 0                                                        |

where N is the number of cascade-inverter levels.

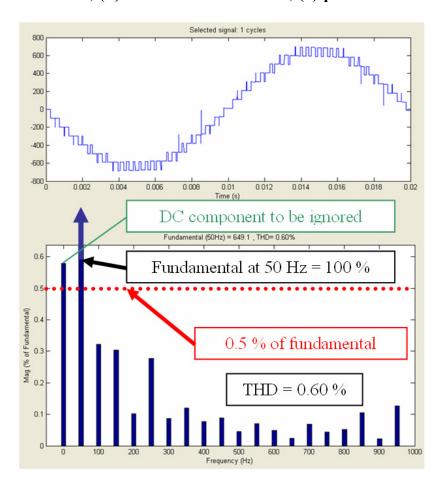

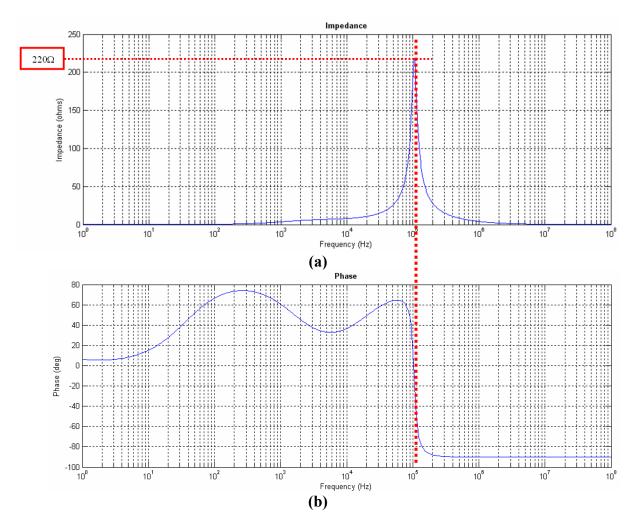

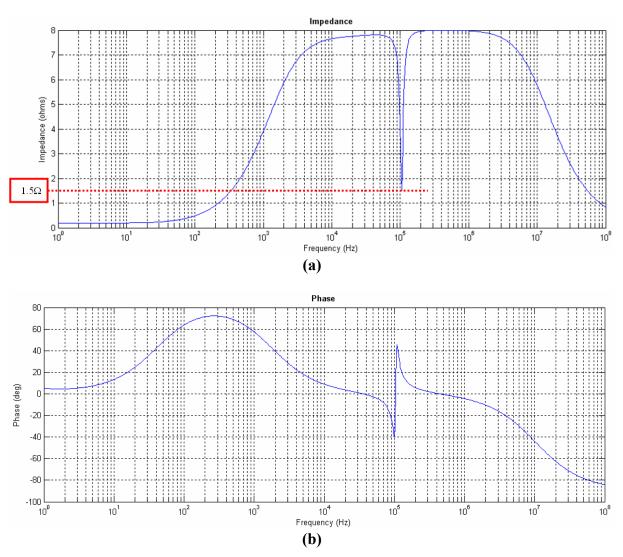

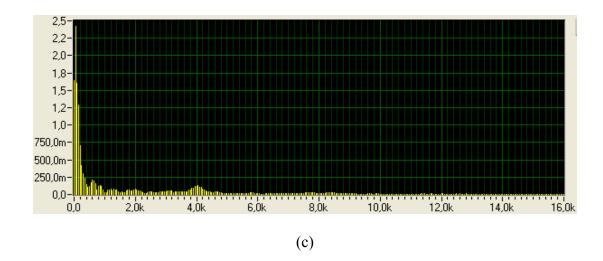

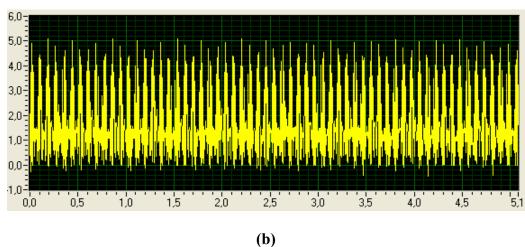

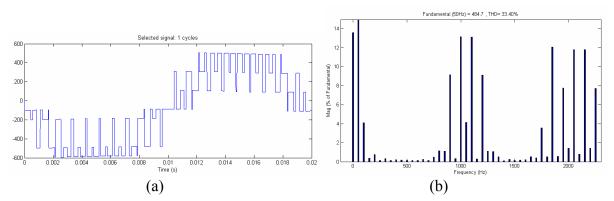

Figure 4-25: Typical phase output frequency spectrum, at a given switch commutation frequency (20 kHz)

In figure 4.25 a triangular carrier has only odd Fourier components, so the output spectrum only has carrier components at odd harmonics of the carrier frequency. The first carrier

components occur at the carrier frequency  $f_c$ . Side-band components occur spaced by  $2 f_0$  from other components, around all multiples of the carrier frequency.

#### 4.2 Power Losses

### 4.2.1 Compact Power Semiconductor Model

In this thesis, MOSFET modules are considered due to the modularity-laboratory power leveland degree of freedom for switching frequencies. For analysis purposes, the MOSFETs and diodes are usually considered ideal, i.e. lossless, featuring infinite current and voltage handling capability. The ideal MOSFET is simulated as being controlled by a logical gate signal ( $g_s \ge 0$ ). It conducts an arbitrary current with zero on-state voltage when the switch is on ( $g_s \ge 0$ ) and blocks any forward or reversely applied voltage with zero current when the switch is off ( $g_s = 0$ ). The idealized device can be switched instantaneously between on and off states or vice versa by applying corresponding gate signals [122].

## 4.2.2 Conduction and Switching Losses

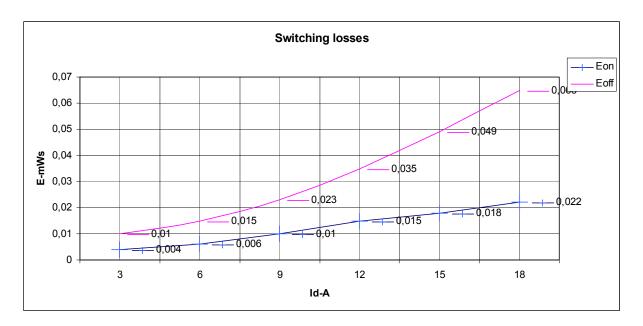

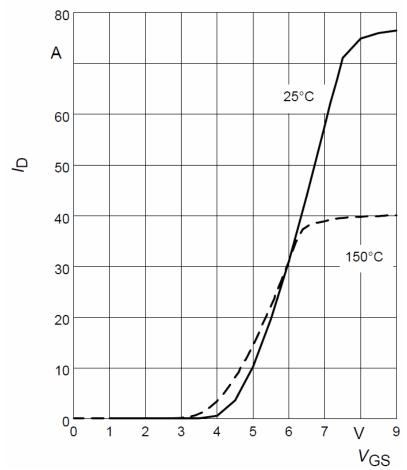

Figure 4-26: Switching losses in power devices (Eon+Eoff). Eon includes SPP20N60C3 diode commutation losses. E = f(Id), inductive load,  $Tj=125^{\circ}\text{C}$ , Vds=380V, Vgs=0/+13V,  $Rg=3.6\Omega$

Switching losses are created by the commutation processes between the different switch states whereas losses in magnetic components as core and copper losses. Only turn-on and turn-off losses of active switches and recovery losses of diodes are considered. Turn-on losses of diodes are usually small so that they can be neglected.

### 4.2.3 Selection of Heat Sinks

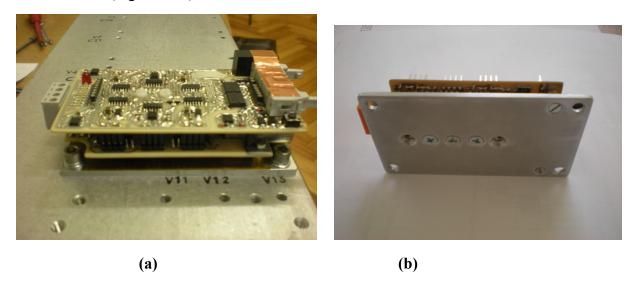

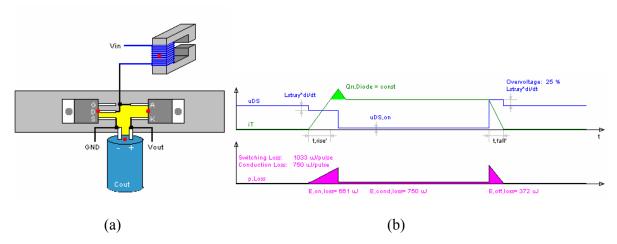

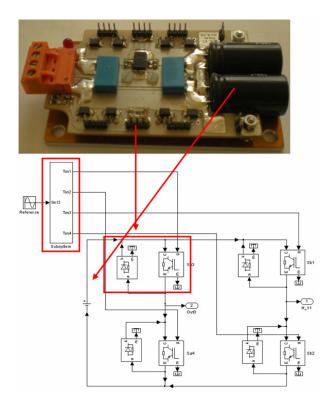

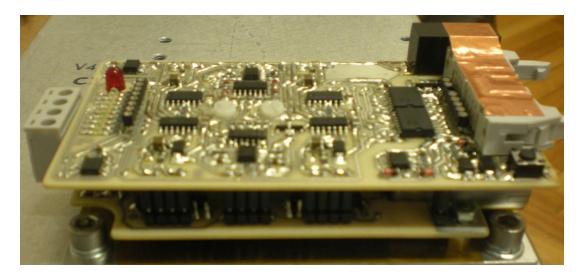

A special standard MOSFET inverter module with switches has been mounted on module cooling plate and driver circuits including protection function has been designed and realized by Wenzel Meier (Figure 4-27).

Figure 4-27: (a) module with switches (b) heat sink of each module

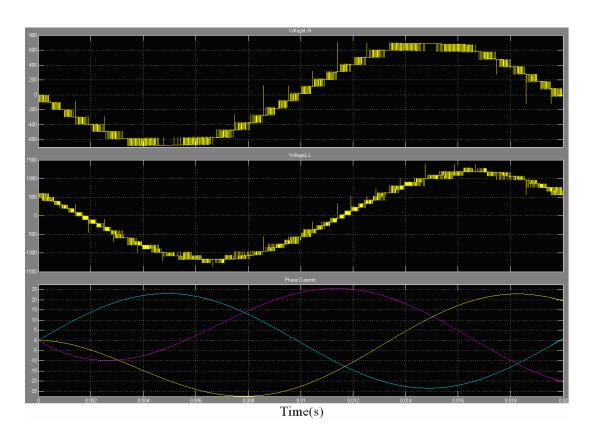

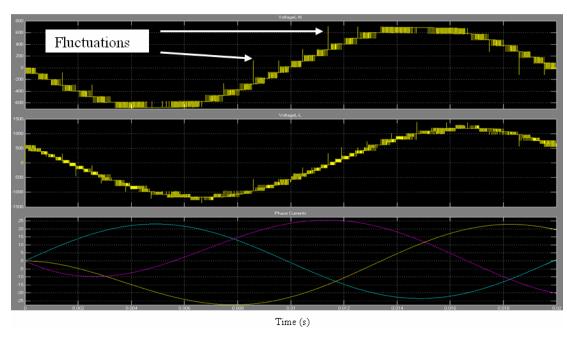

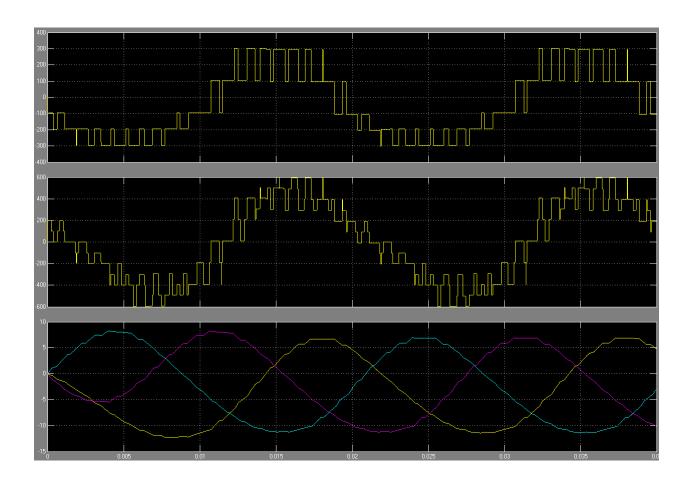

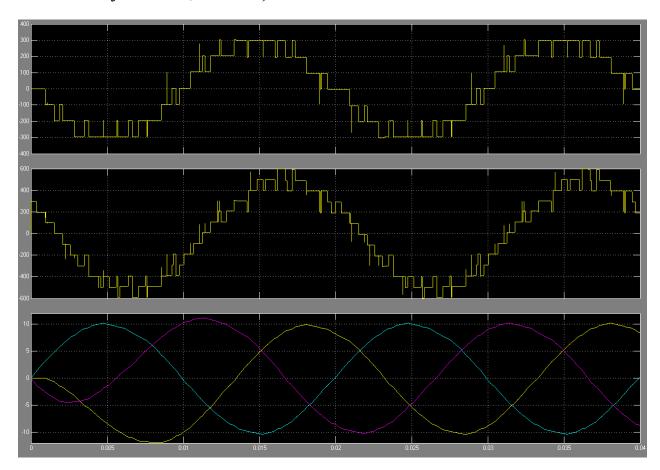

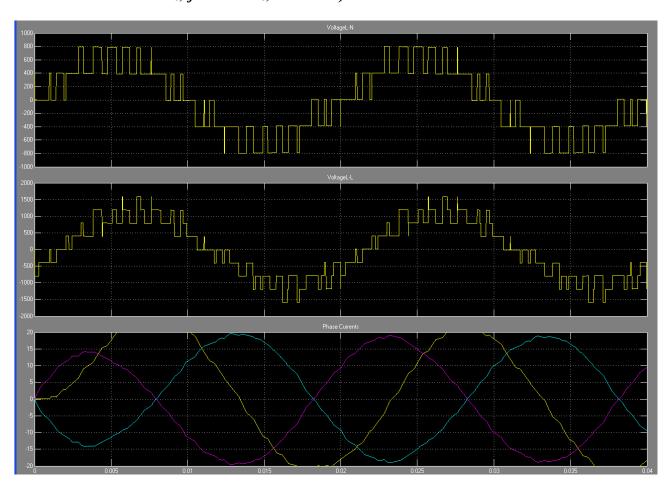

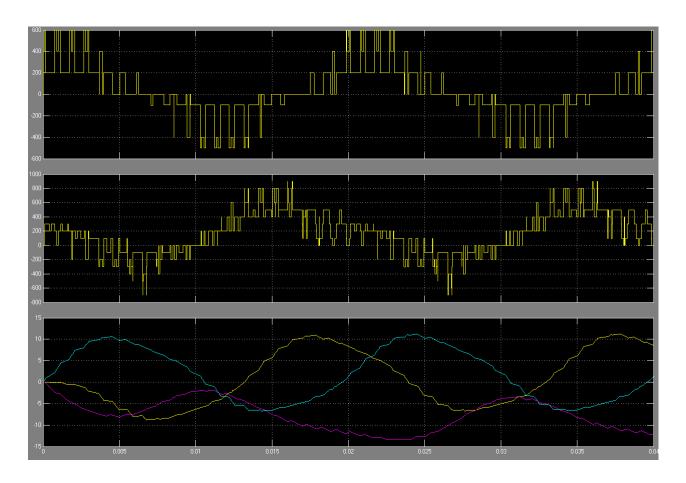

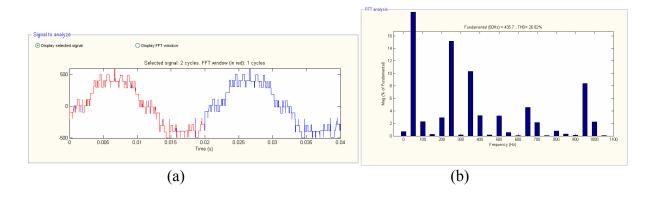

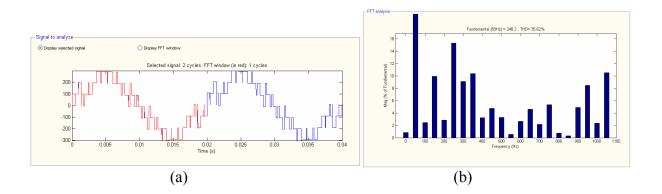

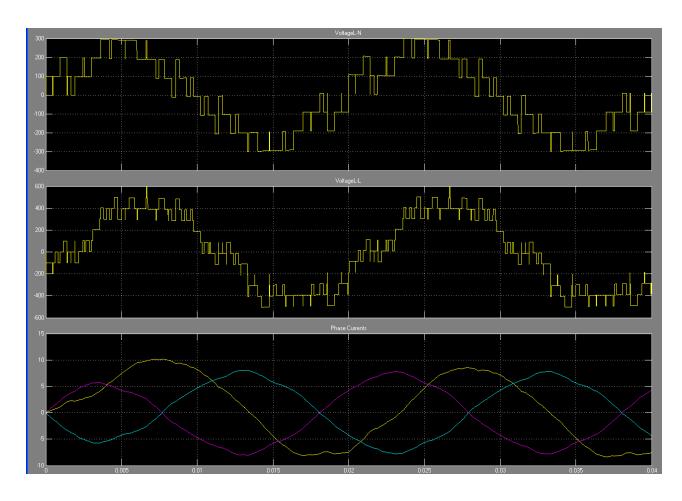

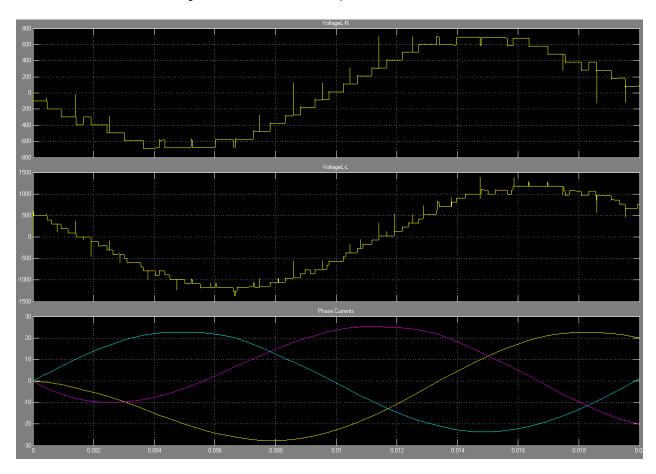

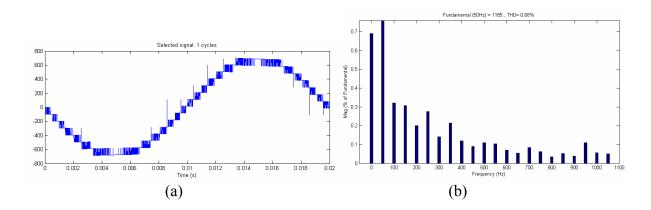

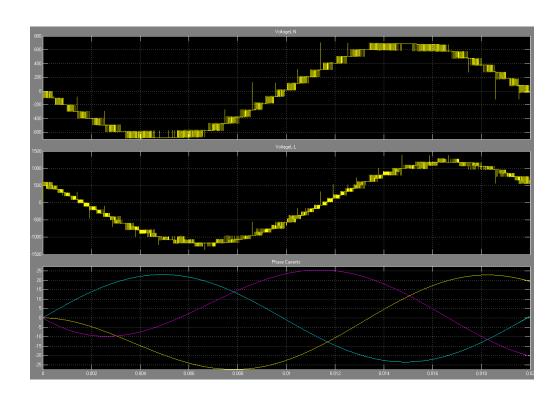

Figure 4-28: PWM control of proposed 2-level inverter at 3 kHz (a) phase waveform, (b) line-to-line waveform, (c) phase currents

Figure 4-29: PWM control of proposed 2-level inverter at 20 kHz (a) phase waveform, (b) line-to-line waveform, (c) phase currents

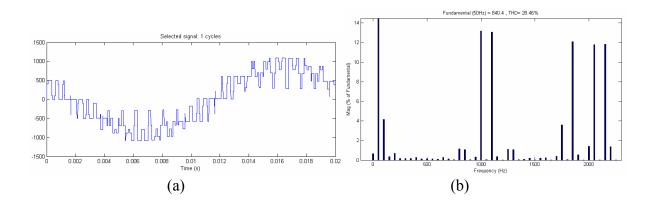

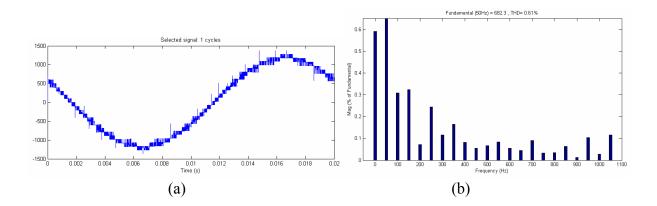

Figure 4-30: Fourier analysis of simulated idealized output voltage at 20 kHz

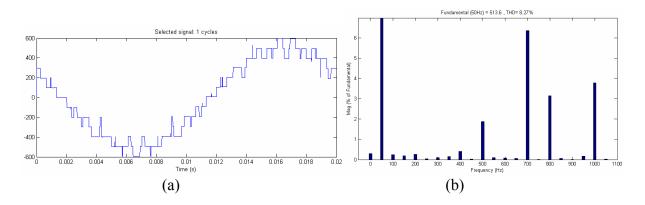

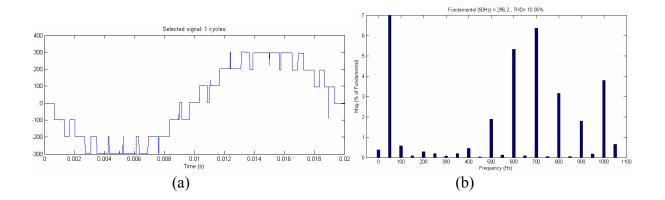

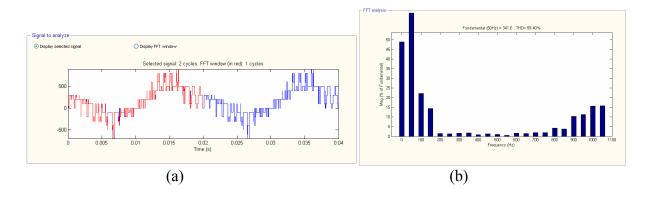

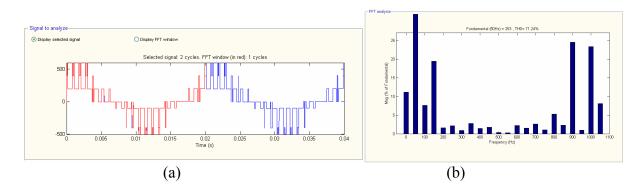

In the control circuit, an eight-bit microcontroller is employed to generate necessary gate drive signals. Due to limited computational capability and control resolution, the experimental

output quality is not as good as expected, especially at low modulation indexes. It should be noted that the level of steps is actually reduced when modulation is less than 0.5. This results agrees the finding in initial analysis in which the convergence fails at M = 0.5: At M = 0.4, the 7 levels become 5 levels, and at M = 0.1, the 7 becomes 3 levels. THD results are obtained for up to 1100 Hz frequencies.

Table 4-7 Specifications of the prototype

| Items                 | Specifications and features |                 |  |  |

|-----------------------|-----------------------------|-----------------|--|--|

| Power MOSFET          | Inverter                    | 650V/20.7A      |  |  |

| Cascaded transformers | EI lamination               | 1:a, 1:2a, 1:4a |  |  |

| Battery $(V_{dc})$    | Oerlikon                    | 12V 50Ah        |  |  |

| Output $(V_o)$        | 8-level PWM                 | AC 230V         |  |  |

The increased resistance, and even more, the increased reactance (due to higher frequency), will result in an increased voltage drop and an increased voltage distortion. THD of current is less than voltage because of filtering effect of L.

Table 4-8 Parameters in the hardware prototype

| Parameter of component                  | Value                                  |

|-----------------------------------------|----------------------------------------|

| Number of series H-bridges at the input | 3                                      |

| Rated power                             | 1400VA                                 |

| Nominal peak input voltage              | 30                                     |

| Primary DC-link voltages                | 030V                                   |

| Output Ph–N voltages                    | $24 V_{rms}$                           |

| Transformers turn ratio                 | 1:8.3                                  |

| Primary DC link capacitors              | 3300μF, 350V                           |

| Fundamental frequency                   | 50Hz                                   |

| Switching frequency                     | 4 kHz20 kHz (suitable for MOSFET only) |

#### 4.3 Conclusion

The measurement is made by current transducer LTS 25-NP that has 3 numbers of primary turns. The voltage drop across load resistor corresponds to the current of a phase.

The function of the proposed inverter and the designed controllers are verified by experimental results on a laboratory scale prototype. The prototype is a 200VA, single-phase transformer. The digital control unit was implemented based on an ATmega16 controller. It is worth noting that low voltage power MOSFETs (MOSFET + internal body diode with the break down voltage of 650 V) was intentionally used in the prototype to demonstrate a scale down of the real situation. However, in the medium voltage levels, the IGBTs would be the best choice due to better output power quality and current ratings.

To verify the simulation results, a quasi-eight-level voltage source converter using cascaded-inverters with the same DC source is used as a hardware prototype. The large power cells

commutate only a few times per cycle. Since the small power cells manage only 14.1% of the total power, a big reduction in switching losses is achieved.

Another major advantage of the SC2LHB is its circuit layout flexibility, because each level has the same structure and there are no extra clamping diodes or voltage balancing capacitors, which are required in the NPC and the FLC topologies. The number of output voltage levels can then be easily adjusted by changing the number of H-bridge cells. However, the control complexity is directly proportional to the number of H-bridge cells. As the number of voltage levels increases, the voltage imbalance problem becomes more of a concern. To achieve stable system, a well-defined model is necessary.

# 5 Modelling and Simulation

# 5.1 Schematic Description of the System

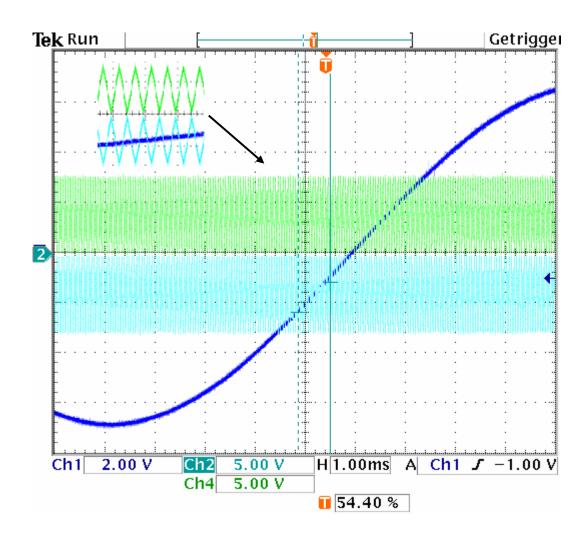

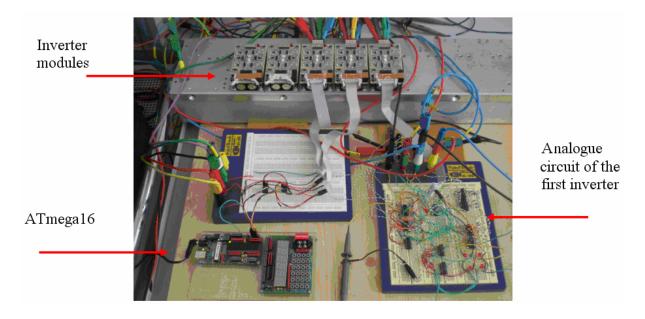

The first prototype was built to check the function of proposed multilevel topology. During the construction of the prototype, several problems have been fixed. The most critical problem concerns the insulation among the three inverters there are in the system. Indeed, if the insulation fails the common mode current will be free to flow and the multilevel will not work properly anymore [70] [71]. The first test had the aim to verify insulation applying switching voltage to only one phase, just to prove the absence of common mode current [28]. Then, some tests were done to see the operation of dual 2-level inverter as multilevel converter. For this purpose, a PWM modulation has been implemented and some screenshots have been captured. The detailed results and configurations are listed in appendix A. This technique allows successful voltage control of the fundamental wave as well as suppression of a selective set of harmonics [44].

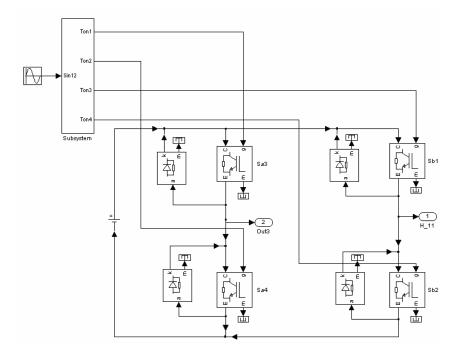

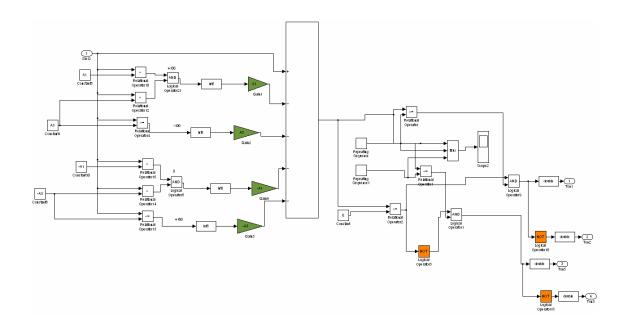

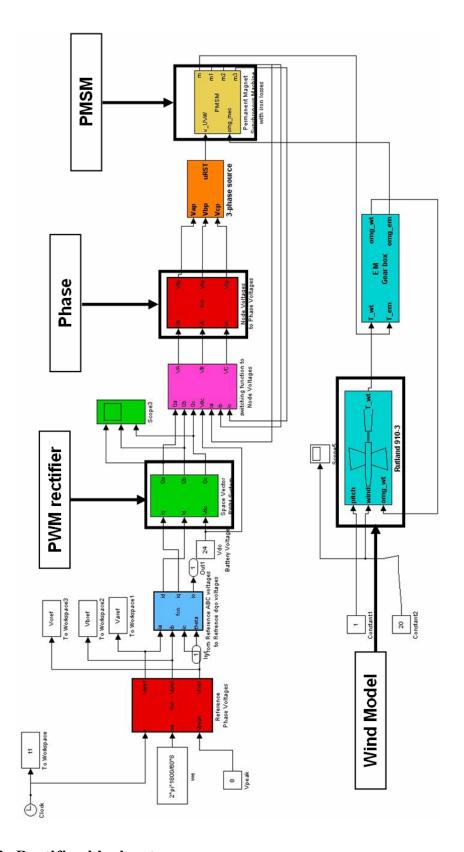

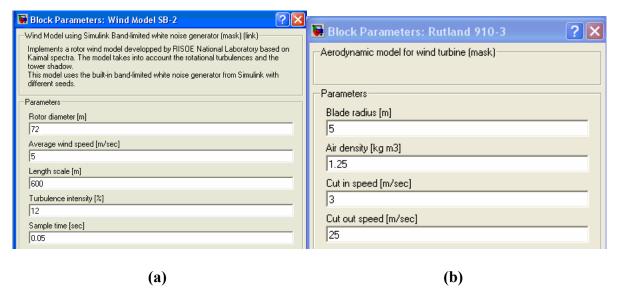

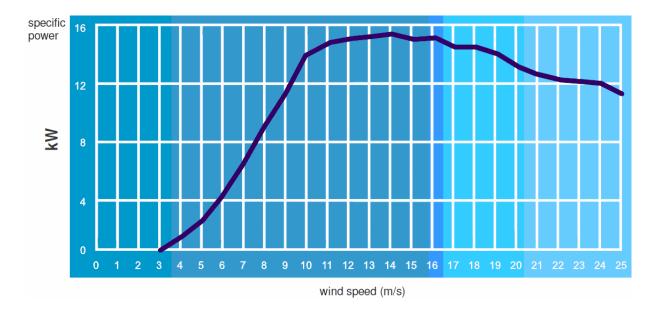

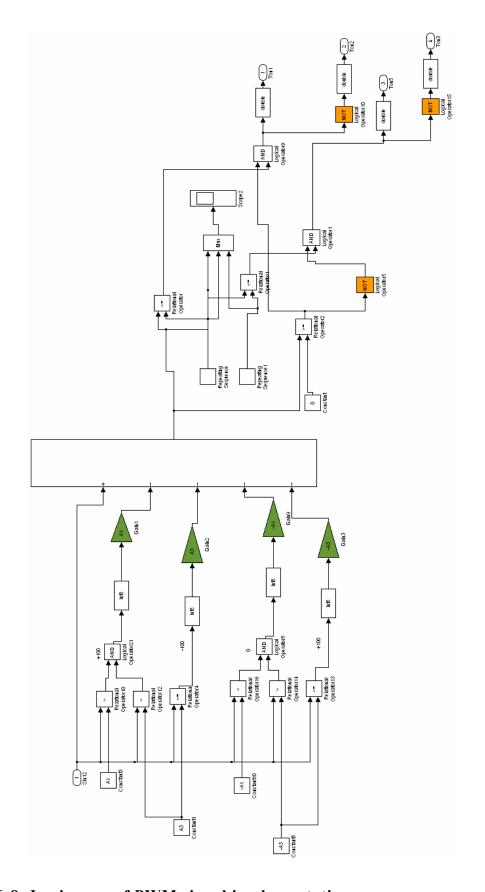

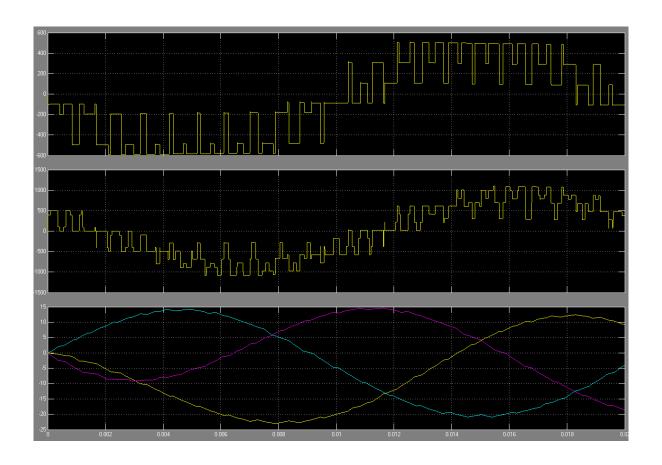

Figure 5-1: MATLAB/SIMULINK model of wind turbine system

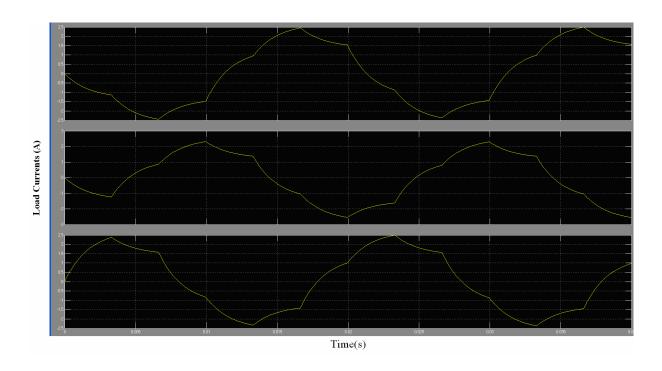

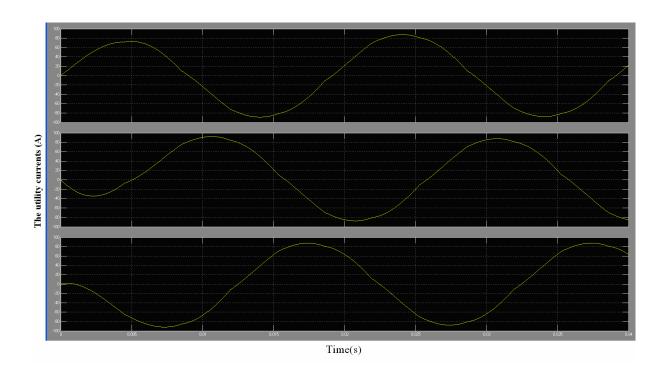

The model of the inverter implemented in MATLAB-SIMULINK is shown in figure 5-1. SIMULINK has been chosen from several simulation tools because its flexibility in working with analogue and digital devices [16] [40]. Mathematical models can be easily incorporated in the simulation and the presence of numerous tool boxes and support guides simplifies the simulation of large system. SIMULINK is capable of showing real time results with reduced simulation time and debugging. The experimental evaluations have led to the following considerations:

- the simulation results have been validate by the experimental results

- the design of the controller is well performed

In the present simulation measurement of currents and voltages in each part of the system is possible, thus permitting the calculation of instantaneous or average losses, efficiency of the drive system and total harmonic distortion [9].

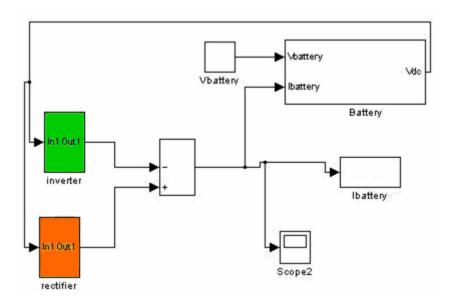

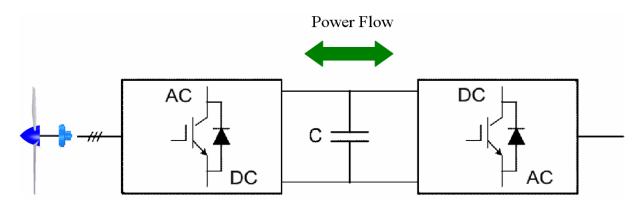

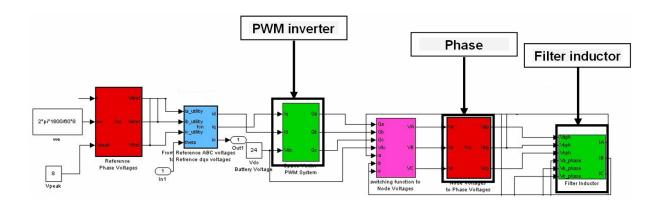

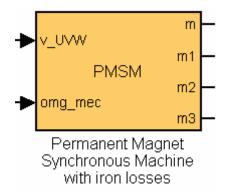

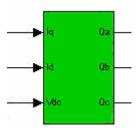

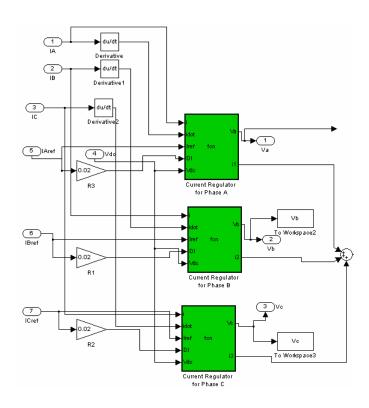

The green block is the 3-phase inverter connected to the two blocks representing the rectifier as shown with orange block and battery. The DC bus has 15 units of 24V batteries connected in series. The two inverters are composed by several masked subsystems. The proposed system consists of three blocks, rectifier, inverter and battery. In rectifier unit, as shown in figure 5-2, there are the wind model, PMSM and rectifier modules. In inverter unit, the inverter, grid and filter blocks are modelled [7]. In order to simulate the entire system for the assessment of the control system, the models of the following items are required:

- model of the PMSM

- model of the rectifier

- model of the DC-link capacitor

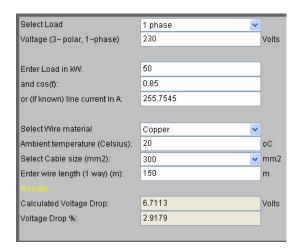

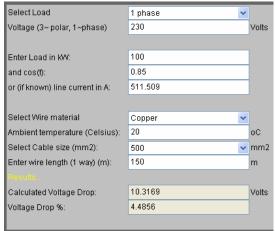

- model of the converter